# Broad-Based Side-Channel Defenses for Modern Processor Architectures

Ashay Rane

Advisors: Calvin Lin and Mohit Tiwari

The University of Texas at Austin

# theguardian

Meltdown and Spectre: 'worst ever' CPU bugs affect virtually all computers

The Washington Post

Huge security flaws revealed — and tech companies can barely keep up

BUSINESS INSIDER

chip maker faces 35 lawsuits over the attacks

Spectre, Meltdown, ...

Spectre, Meltdown, ...

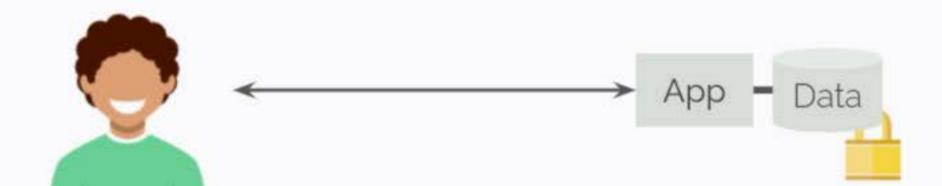

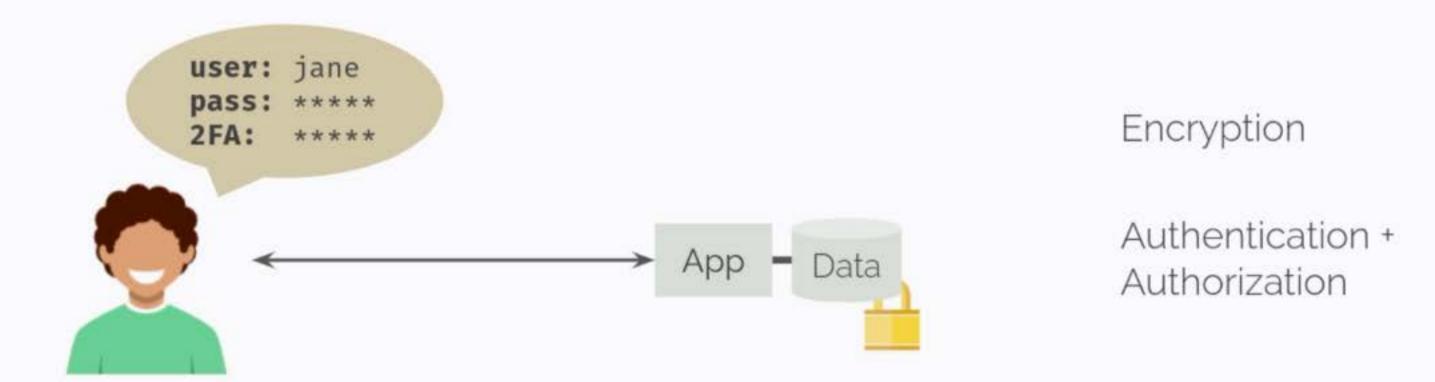

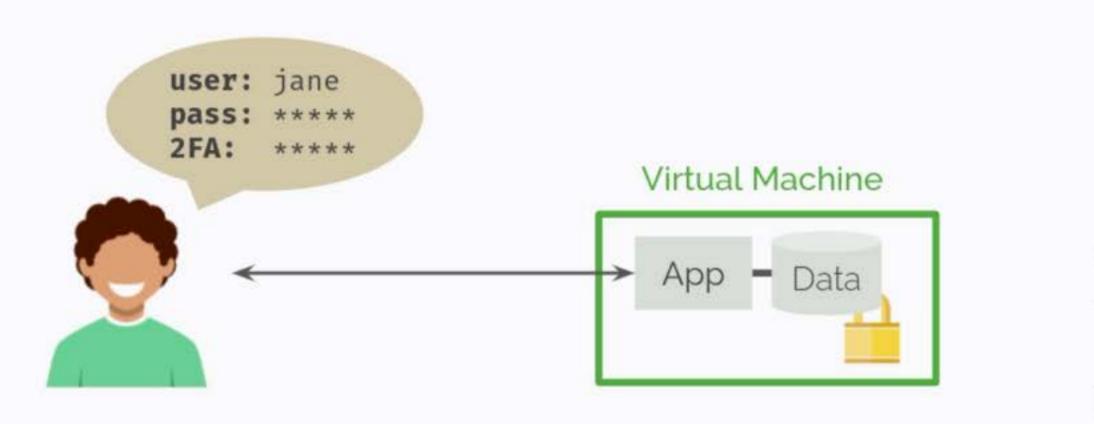

# Private Information in Various Applications

## Private Information in Various Applications

We want to prevent leakage of private information

Encryption

Encryption

Authentication + Authorization

Sandboxing

Encryption

Authentication + Authorization

Sandboxing

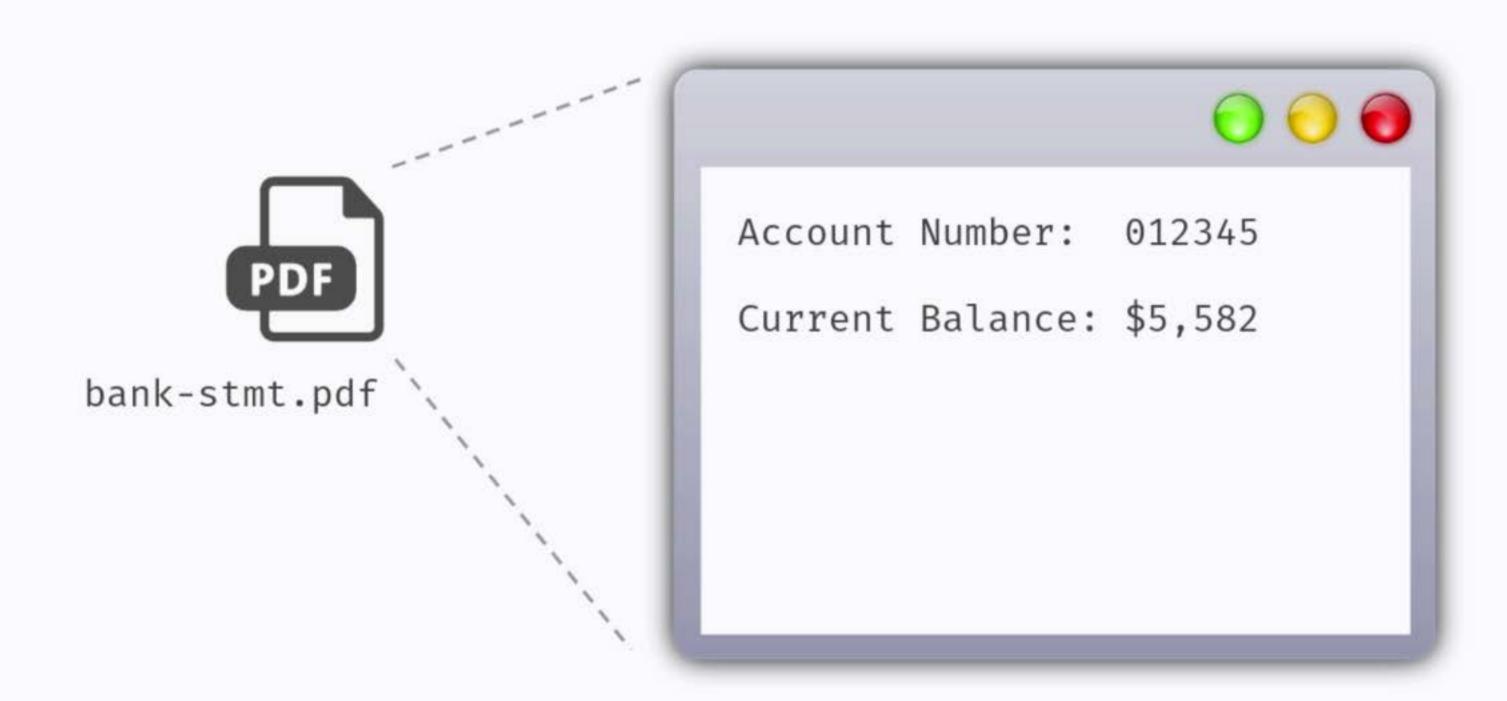

# Example Scenario

bank-stmt.pdf

# Example Scenario

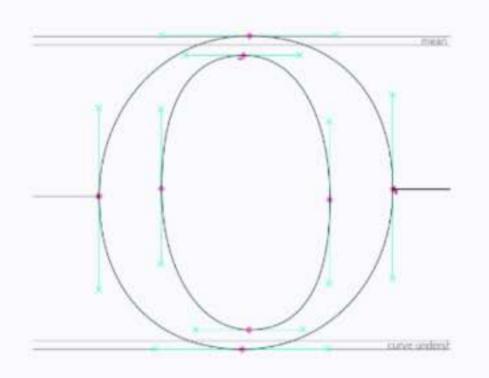

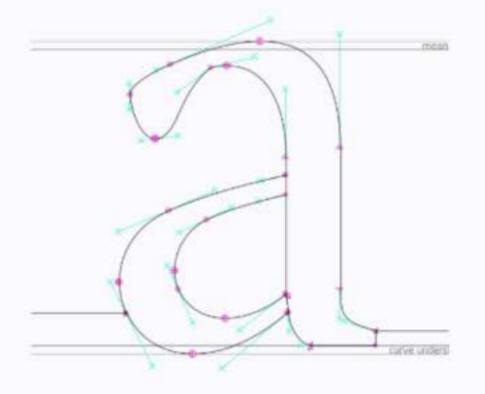

a

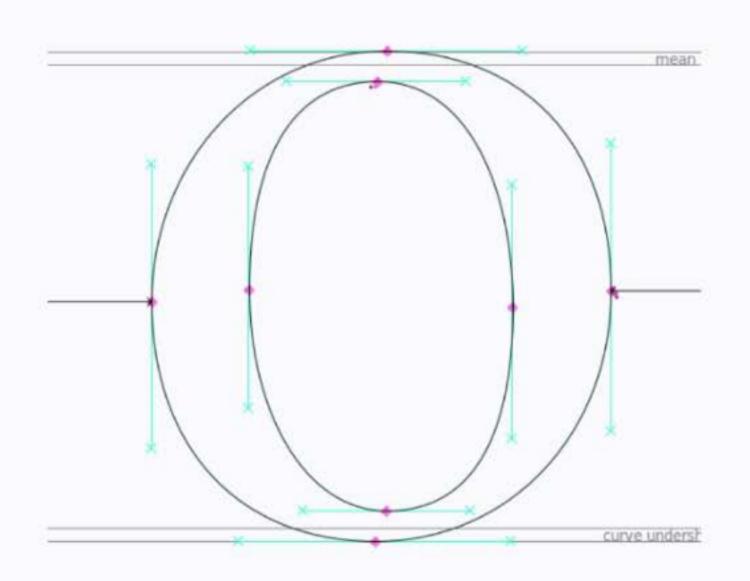

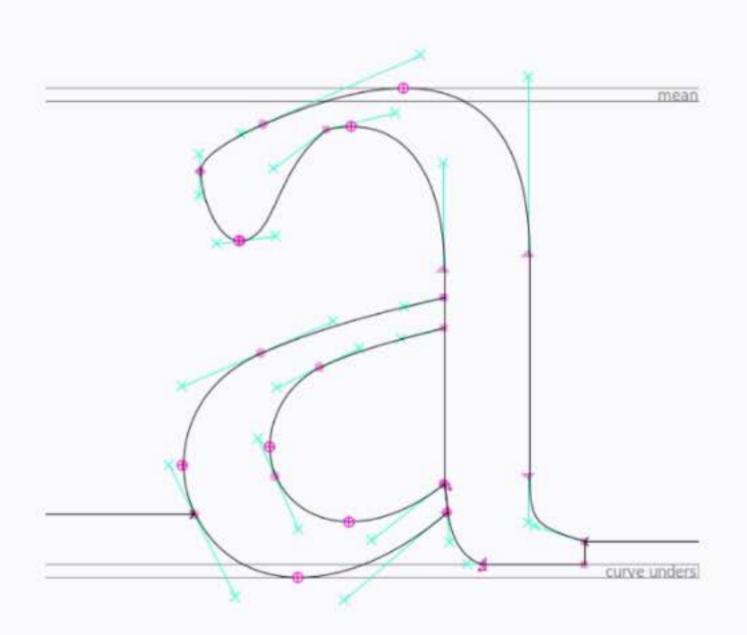

Rendered using lines and curves

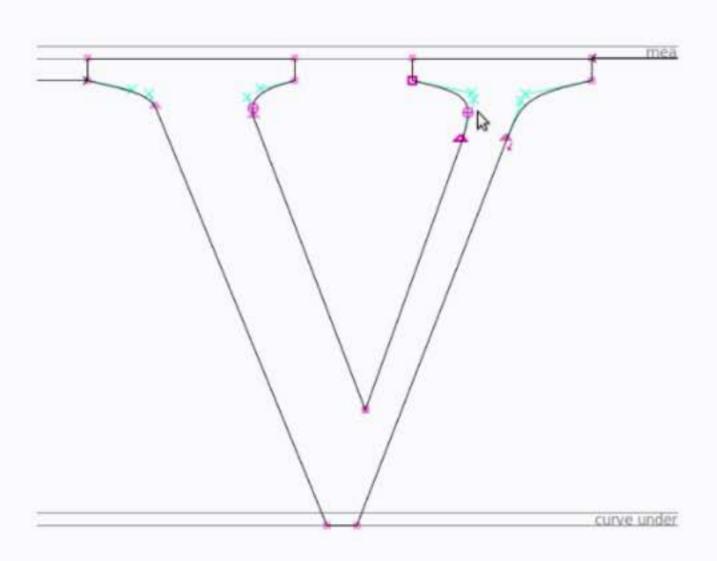

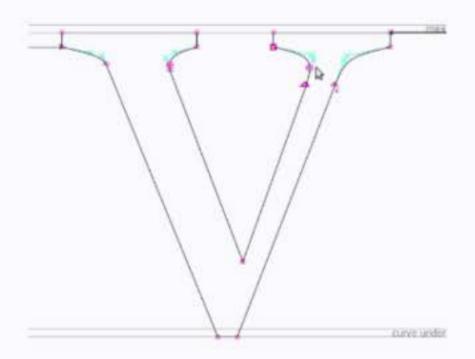

V

Rendered using lines and curves

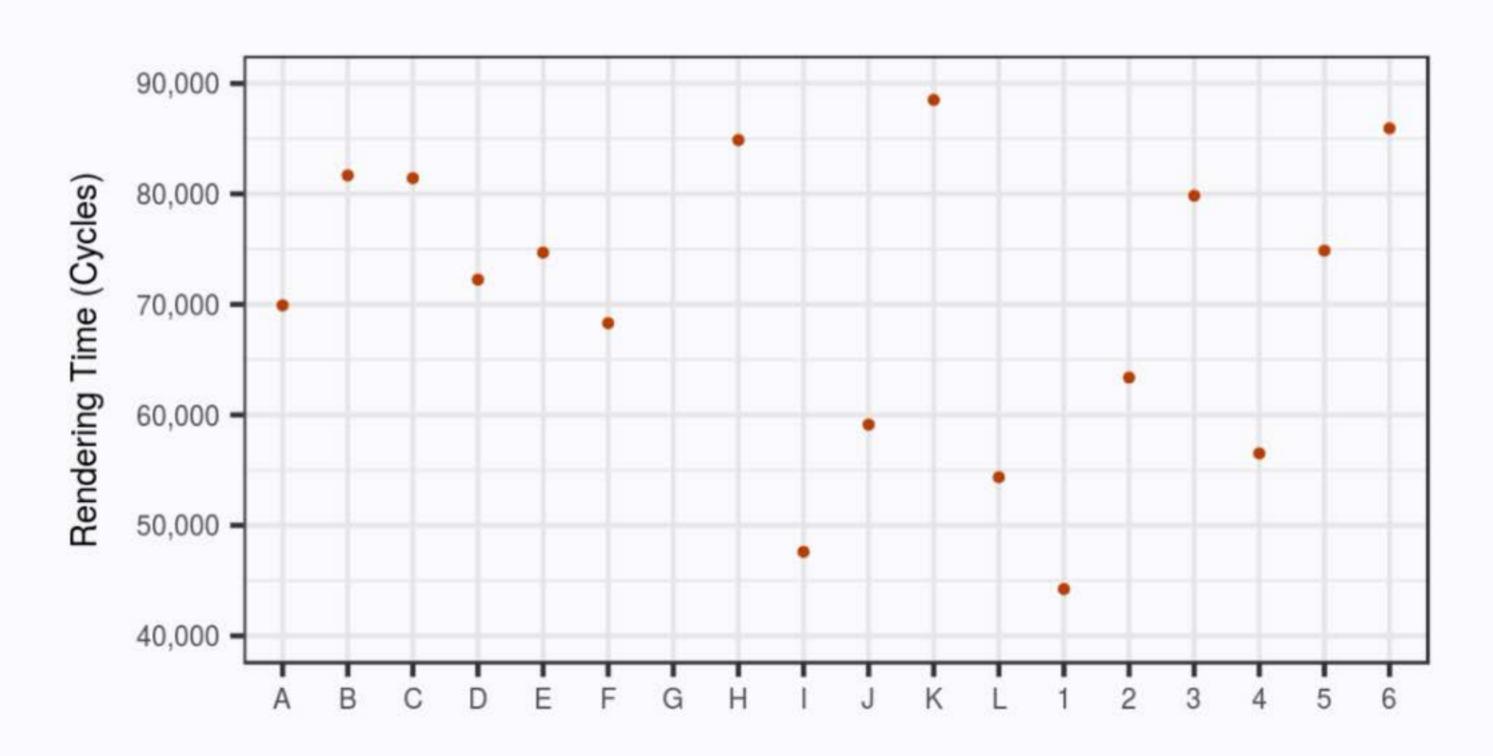

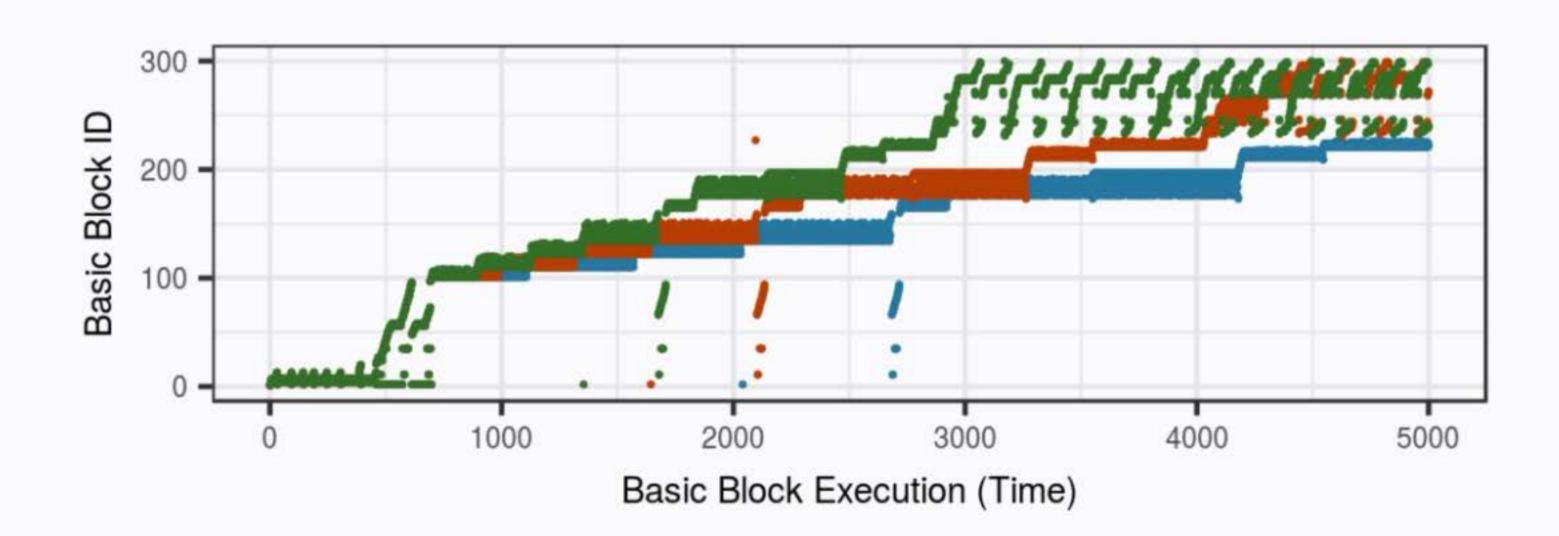

# Execution Time for Rendering Characters

#### Original Text:

hello world my social security number is 123 45 6789

Original Text:

hello world my social security number is 123 45 6789

Recovered Text:

#### Original Text:

hello world my social security number is 123 45 6789

#### Recovered Text:

wello would my socqal secuuqtk kumweu it 1r3 45 6789

#### Original Text:

```

hello world my social security number is 123 45 6789

```

Recovered Text:

```

wello would my socgal secuuqtk kumweu it 1r3 45 6789

```

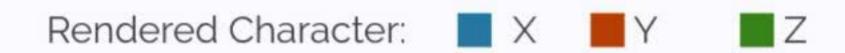

41 out of 52 characters correctly guessed

Attacker can measure execution time to steal sensitive document contents

[Xu et al., Oakland-2015]

Application converts document into an image

[Xu et al., Oakland-2015]

Application converts document into an image

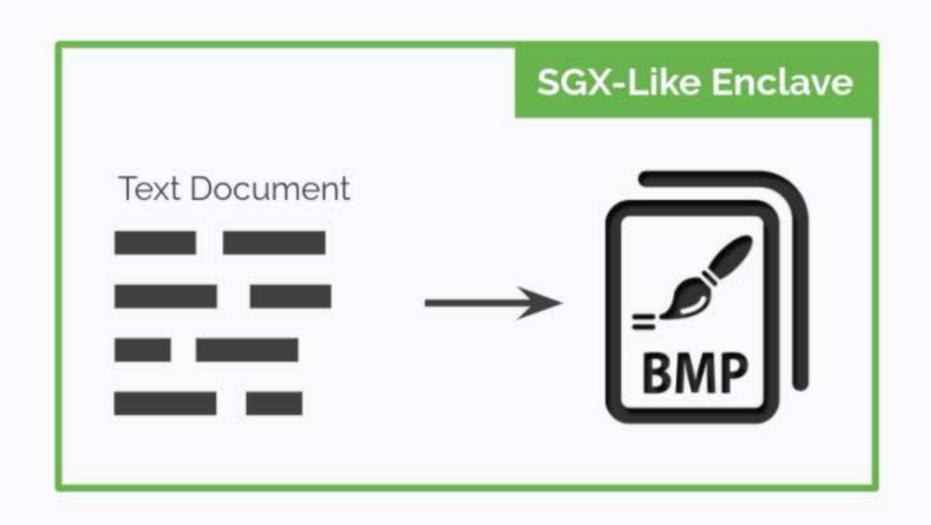

Application runs inside an SGX-like enclave

[Xu et al., Oakland-2015]

Application converts document into an image

Application runs inside an SGX-like enclave

Malicious OS observes page faults

**Malicious Operating System**

[Xu et al., Oakland-2015]

Application converts document into an image

Application runs inside an SGX-like enclave

Malicious OS observes page faults

**Malicious Operating System**

100% text recovered by OS

# Memory Address Trace While Rendering Characters

### Instruction Trace While Rendering Characters

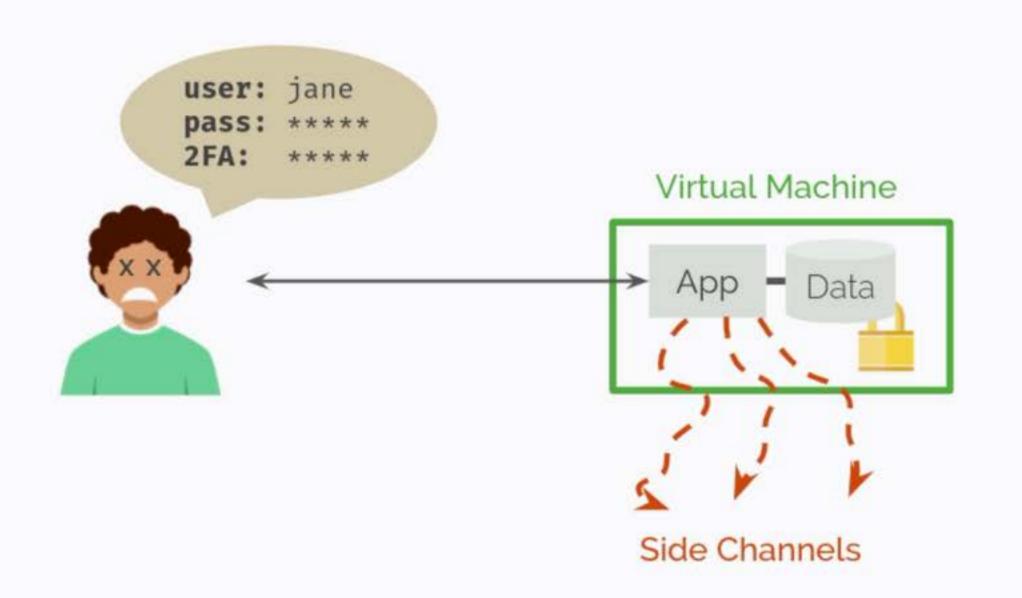

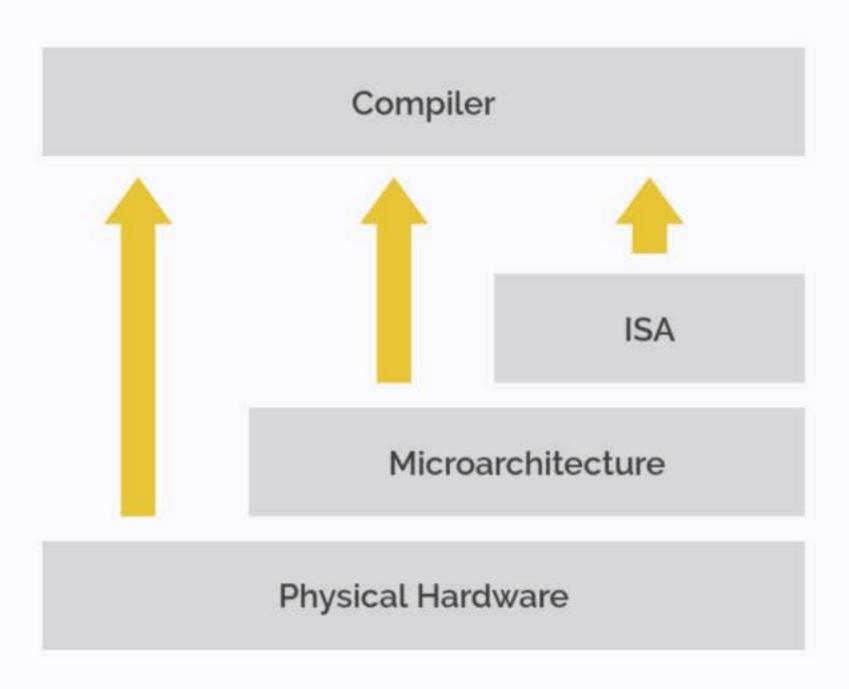

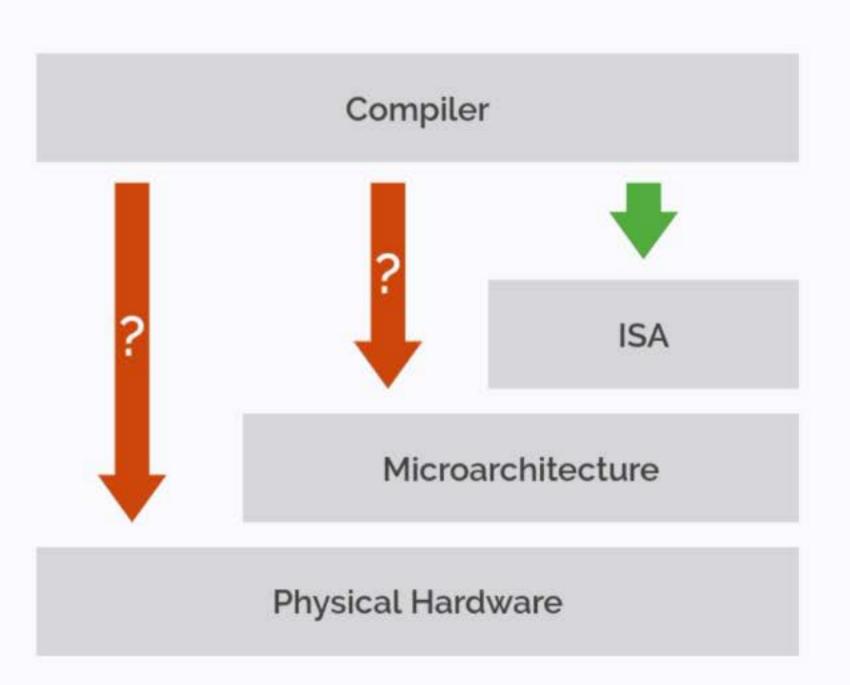

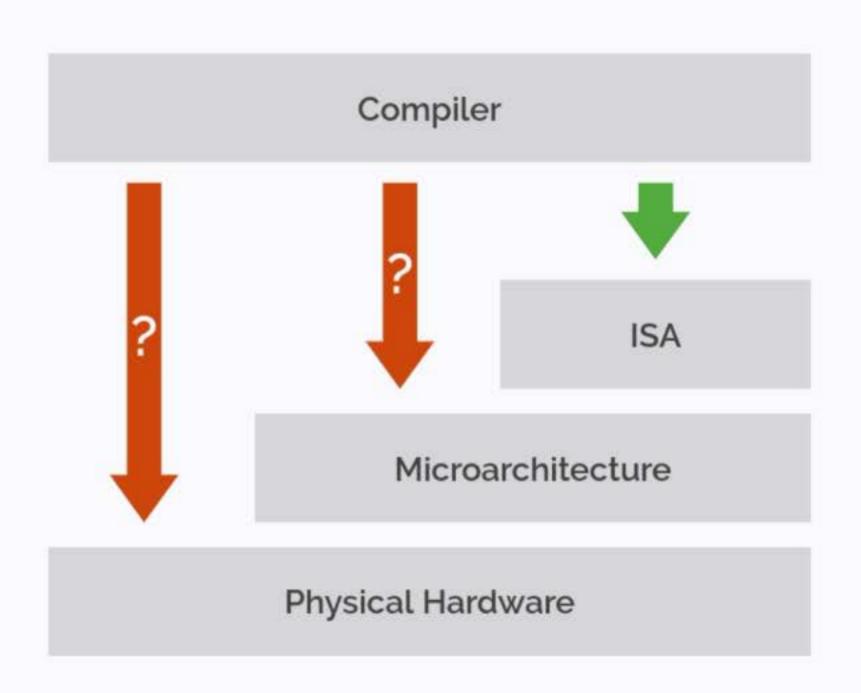

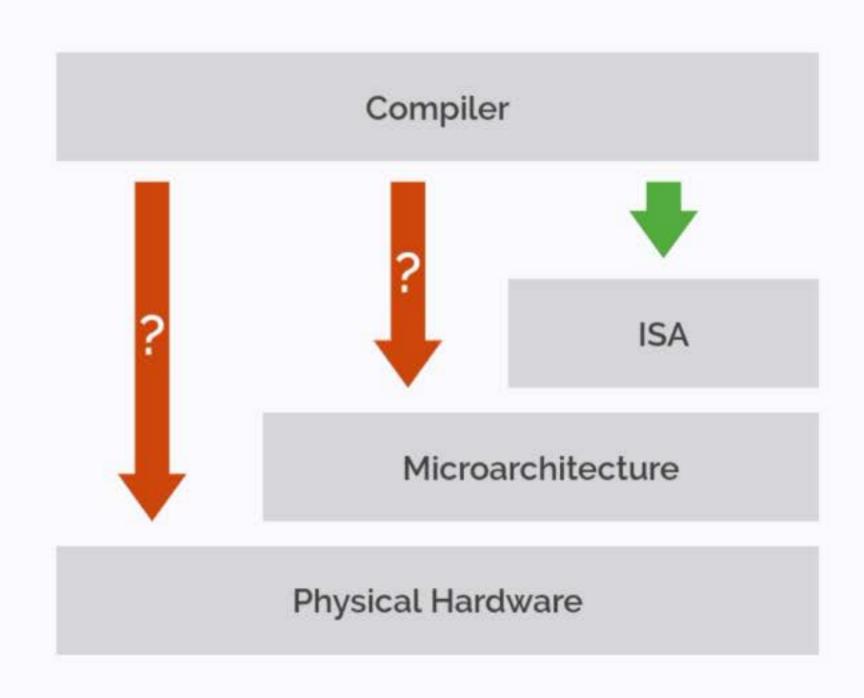

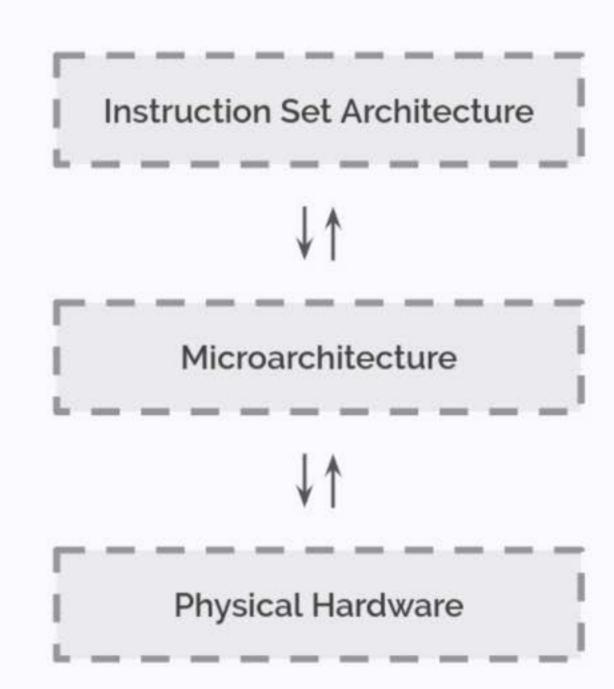

# Information May Leak Through Many Side Channels

**Application Program**

e.g. execution time

Instruction Set Arch

e.g. page faults

Microarchitecture

e.g. branch predictor, cache, PC, DRAM addresses

Physical Hardware

# What is the Core Vulnerability?

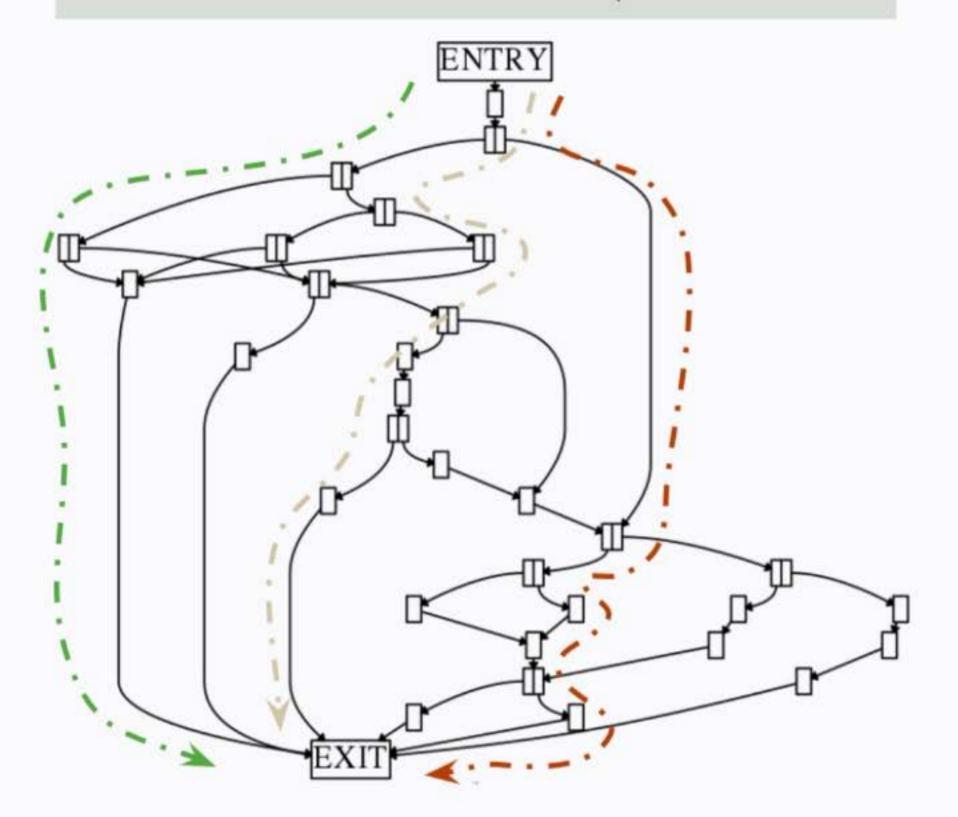

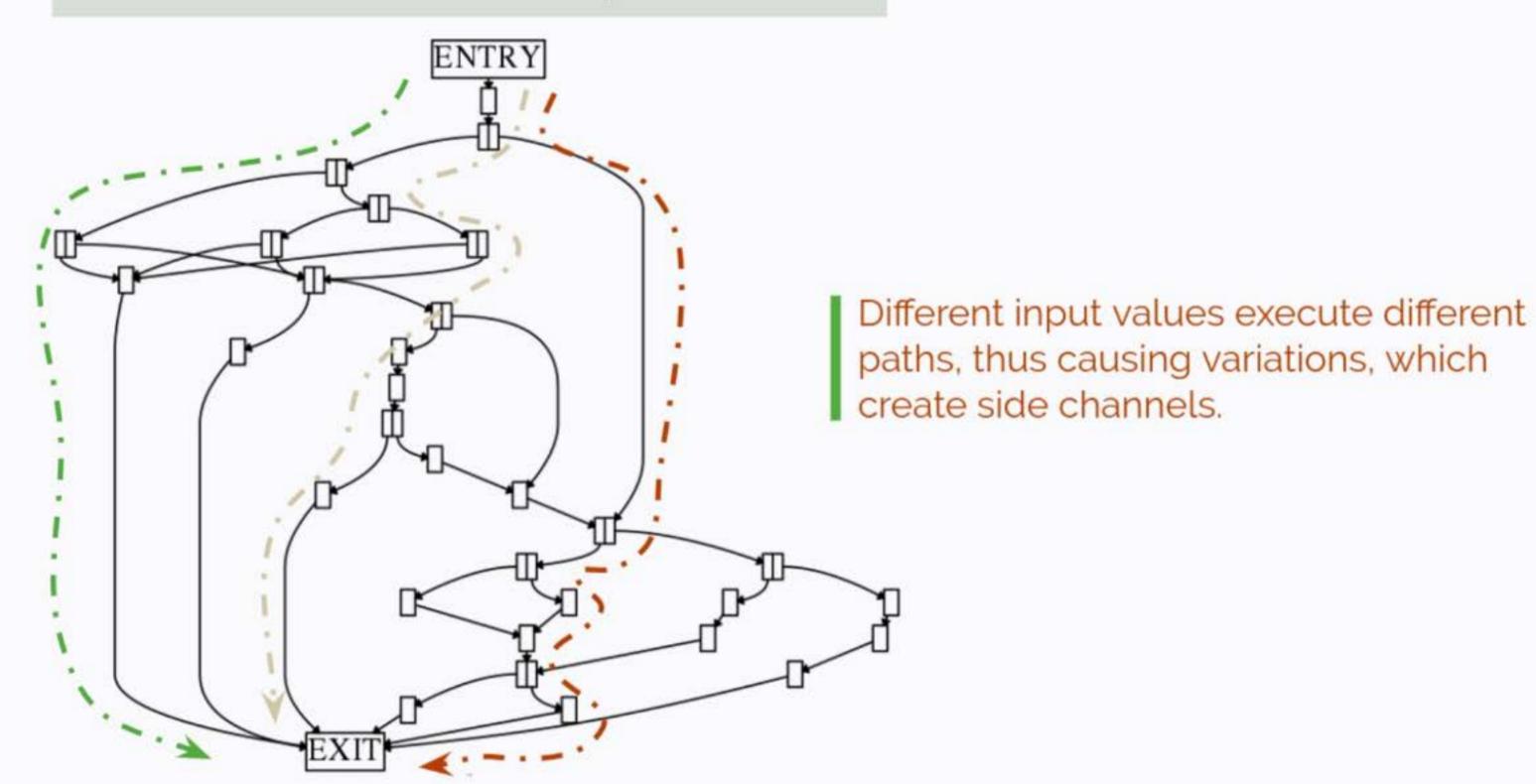

#### Control Flow Graph

#### Control Flow Graph

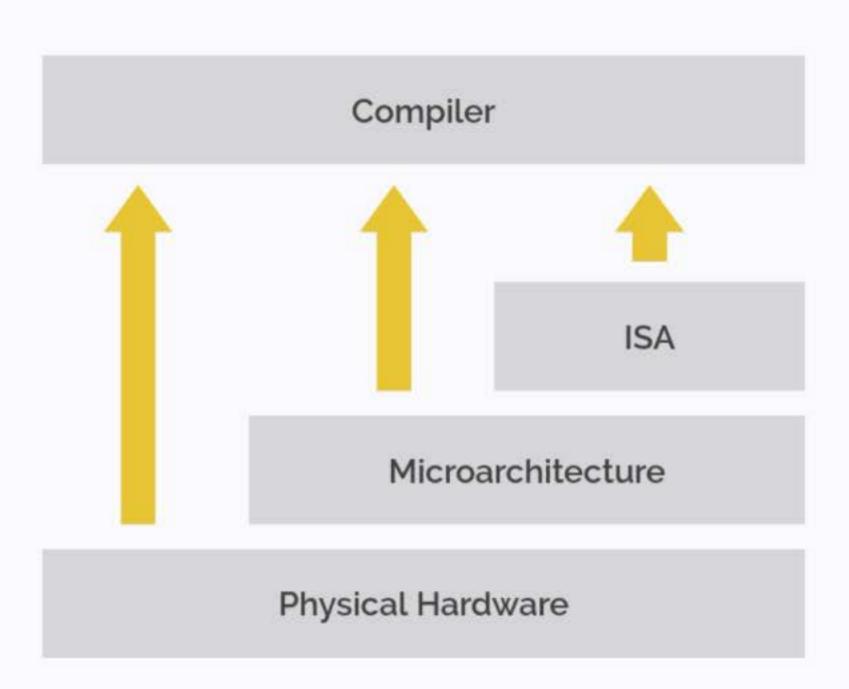

#### Prior Side Channel Defenses

Focus on symptoms, thus providing point solutions

**Application Program**

e.g. execution time

[ISCA12], [ASPLOS15], [CHES00], [ICISC03], [ICISC05], [ICISC10]

Instruction Set Arch

e.g. page faults

Microarchitecture

e.g. branch predictor, cache, PC, DRAM addresses

Physical Hardware

#### Prior Side Channel Defenses

Focus on symptoms, thus providing point solutions

**Application Program**

e.g. execution time

Instruction Set Arch

e.g. page faults

Microarchitecture

e.g. branch predictor cache PC, DRAM addresses [ISCA07], [ISCA08], [HPCA09], [NDSS15], [CCS13a]

Physical Hardware

#### Prior Side Channel Defenses

Focus on symptoms, thus providing point solutions

**Application Program**

e.g. execution time

Instruction Set Arch

e.g. page faults

Microarchitecture

e.g. branch predictor, cache, PC, DRAM addresses

Physical Hardware

[ISCA13], [CCS13b], [CCS13c], [ASIACRYPT11]

1. Focused on the symptoms not the root cause

Requires a completely redesigned solution for every side channel

- Focused on the symptoms not the root cause

Requires a completely redesigned solution for every side channel

- Difficult to ensure end-to-end or comprehensive security

One point solution may negate the security guarantees of another

- Focused on the symptoms not the root cause

Requires a completely redesigned solution for every side channel

- Difficult to ensure end-to-end or comprehensive security

One point solution may negate the security guarantees of another

- 3. Require disabling of optimizations in the compiler and thus, require redesigning the processor for each side channel Since optimizations may break security guarantees

GhostRider [ASPLOS-15]

#### **Original** Program

```

if (secret == 0) {

x <- load ptr_1

y <- load ptr_2

} else {

z <- load ptr_3

}</pre>

```

GhostRider [ASPLOS-15]

#### Original Program

```

if (secret == 0) {

x <- load ptr_1

y <- load ptr_2

} else {

z <- load ptr_3

}</pre>

```

Ensure equal load instructions of each path

#### **Transformed** Code

```

if (secret == 0) {

x <- load ptr_1

y <- load ptr_2

} else {

z <- load ptr_3

d <- load dummy

}</pre>

```

GhostRider [ASPLOS-15]

#### Original Program

```

if (secret == 0) {

x <- load ptr_1

y <- load ptr_2

} else {

z <- load ptr_3

}</pre>

```

Ensure equal load instructions of each path

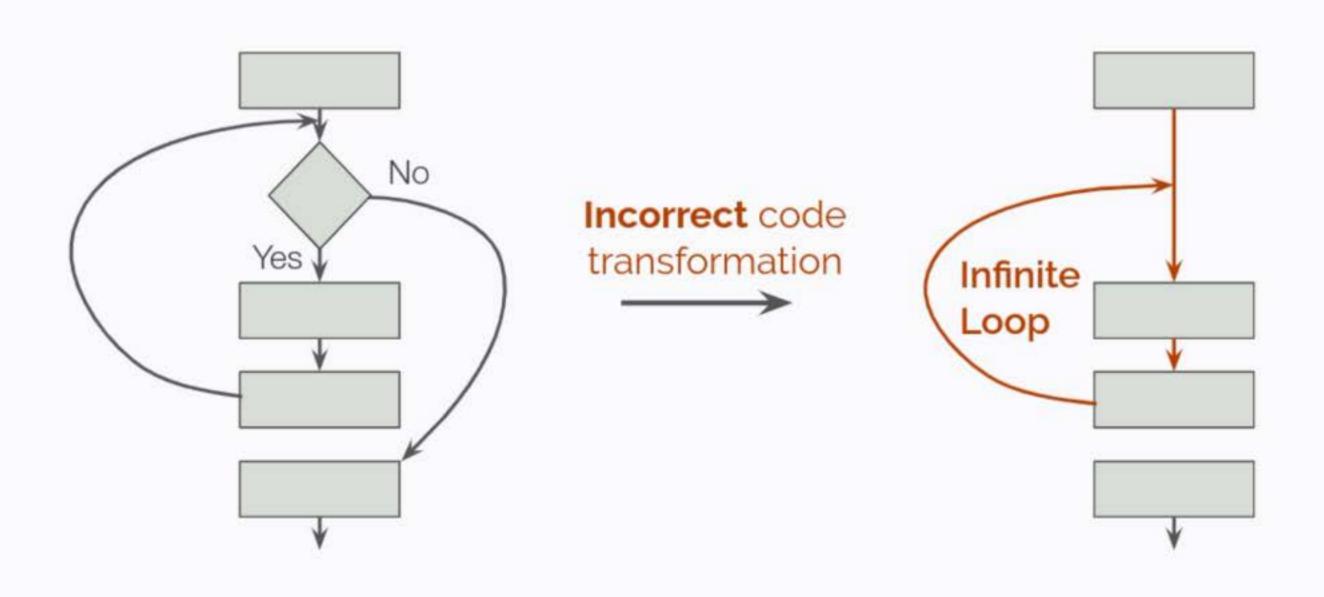

Dead Code Elimination

#### **Transformed** Code

```

if (secret == 0) {

x <- load ptr_1

y <- load ptr_2

} else {

z <- load ptr_3

d < load dummy

}</pre>

```

GhostRider [ASPLOS-15]

#### Optimizing compilers may break the security guarantee

#### **Original** Program

```

if (secret == 0) {

x <- load ptr_1

y <- load ptr_2

} else {

z <- load ptr_3

}</pre>

```

Ensure equal load instructions of each path

Dead Code Elimination

#### **Transformed** Code

```

if (secret == 0) {

x <- load ptr_1

y <- load ptr_2

} else {

z <- load ptr_3

d < load dummy

}</pre>

```

GhostRider [ASPLOS-15]

#### Original Program

```

if (secret == 0) {

x <- load ptr_1

y <- load ptr_2

} else {

z <- load ptr_3

}</pre>

```

Ensure equal load instructions of each path

```

if (secret == 0) {

x <- load ptr_1 Cache hit

y <- load ptr_2 Cache hit

} else {

z <- load ptr_3 Cache hit

d <- load dummy

}</pre>

```

GhostRider [ASPLOS-15]

#### Original Program

```

if (secret == 0) {

x <- load ptr_1

y <- load ptr_2

} else {

z <- load ptr_3

}</pre>

```

Ensure equal load instructions of each path

# if (secret == 0) { x <- load ptr\_1 Cache hit y <- load ptr\_2 Cache hit } else { z <- load ptr\_3 Cache hit d <- load dummy }</pre>

GhostRider [ASPLOS-15]

#### Caches and prefetchers may break the security guarantee

# if (secret == 0) { x <- load ptr\_1 y <- load ptr\_2 } else { z <- load ptr\_3 }</pre>

Ensure equal load instructions of each path

```

if (secret == 0) {

x <- load ptr_1 Cache hit

y <- load ptr_2 Cache hit

} else {

z <- load ptr_3 Cache hit

d <- load dummy Miss!

}</pre>

```

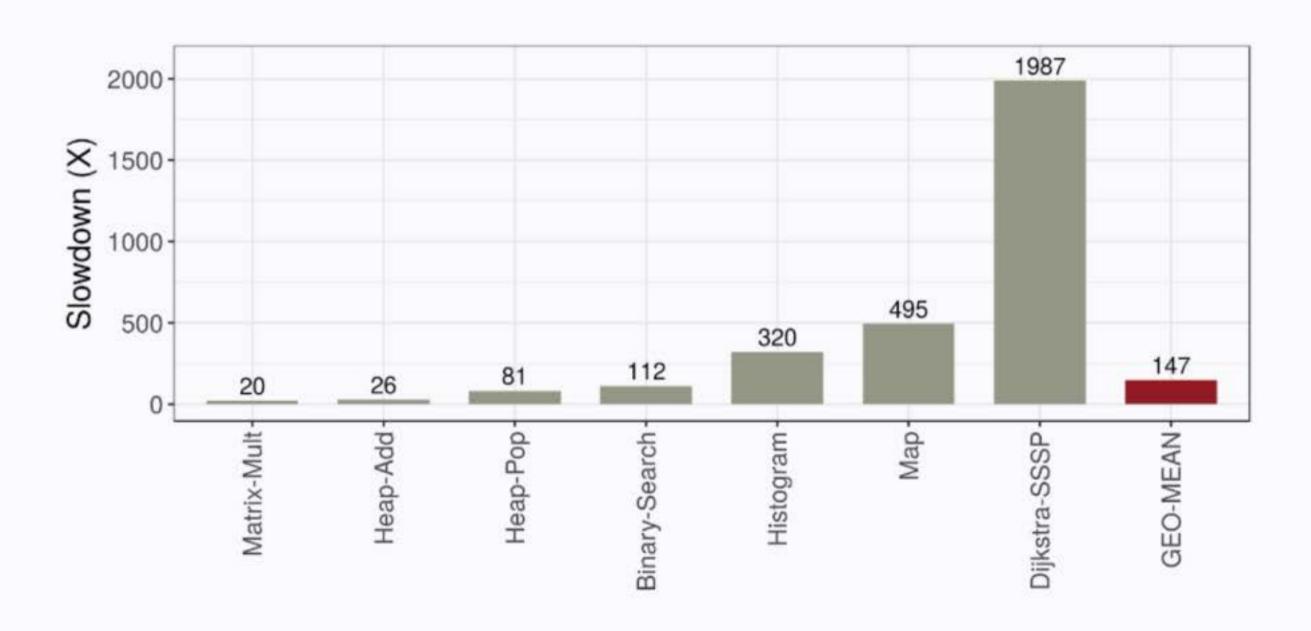

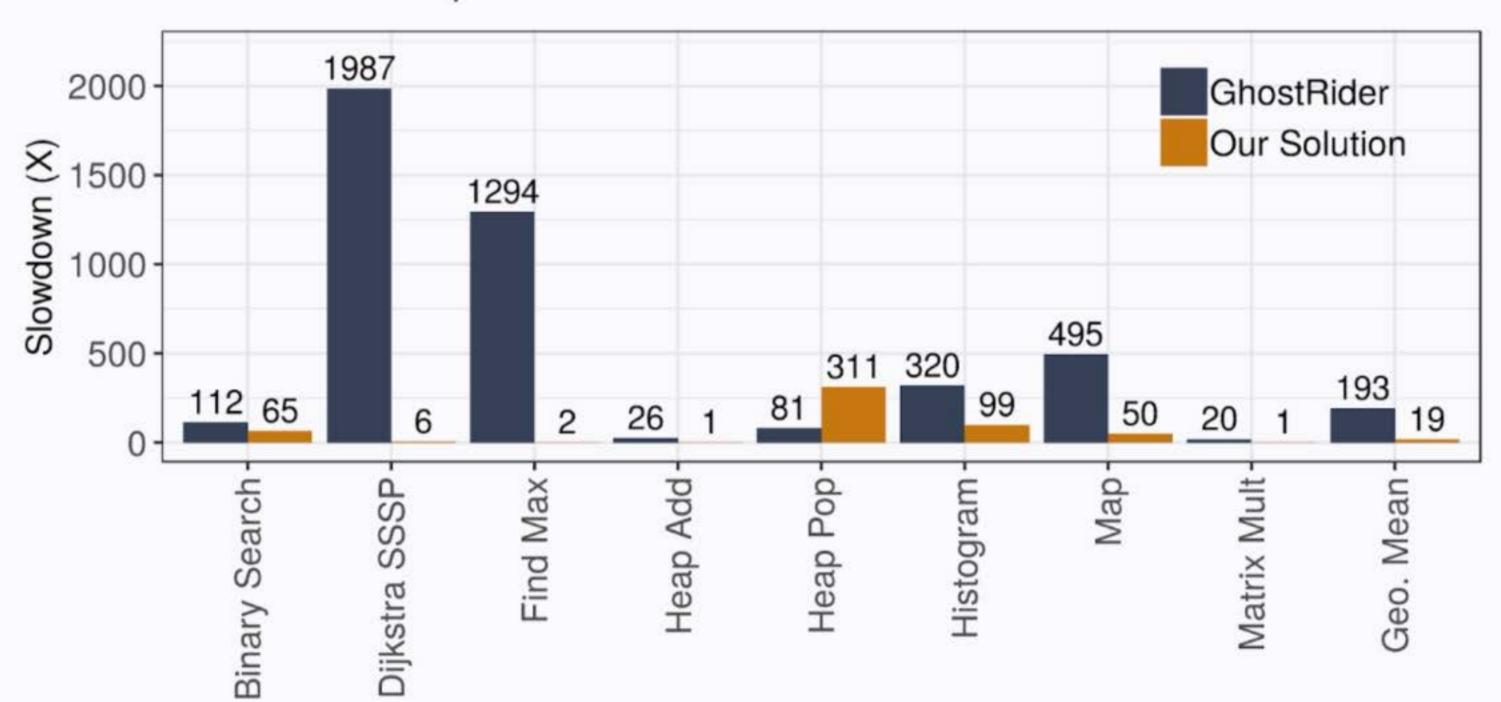

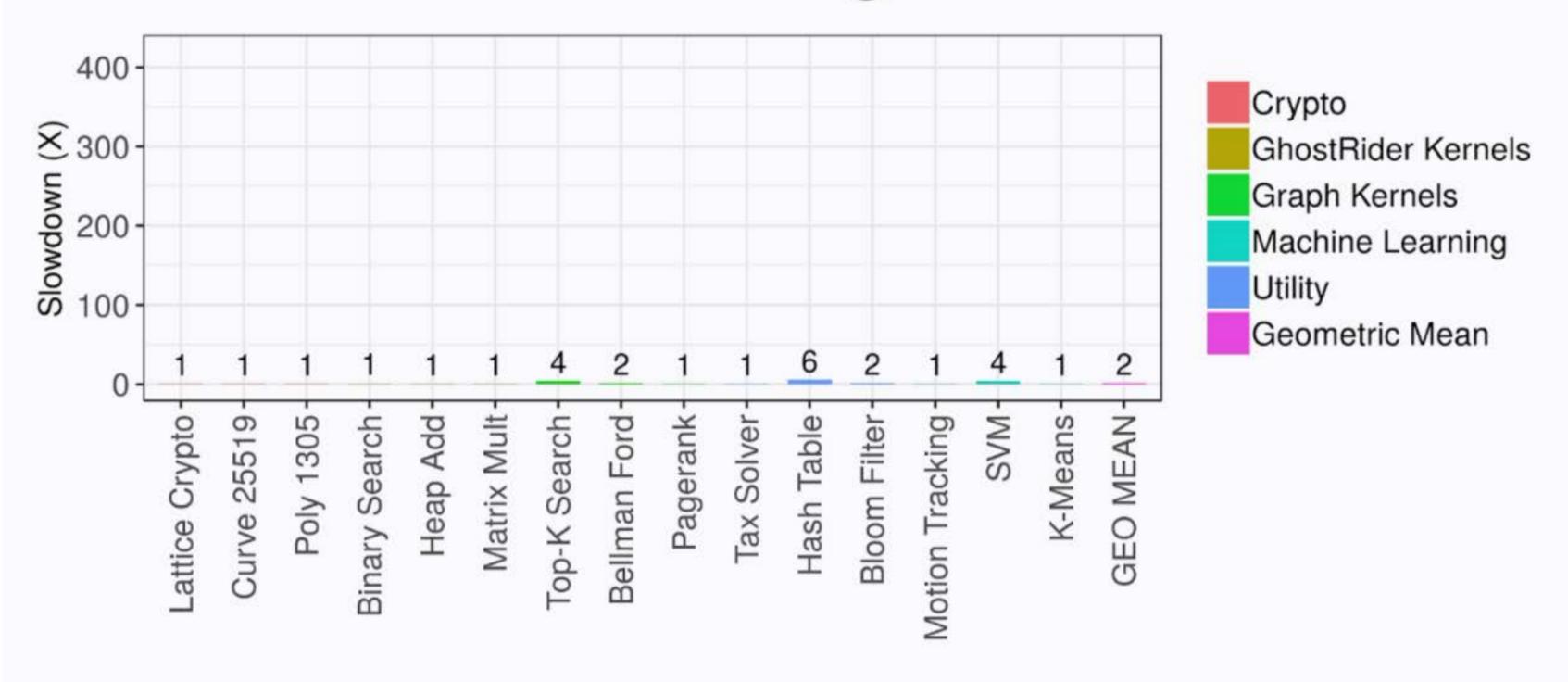

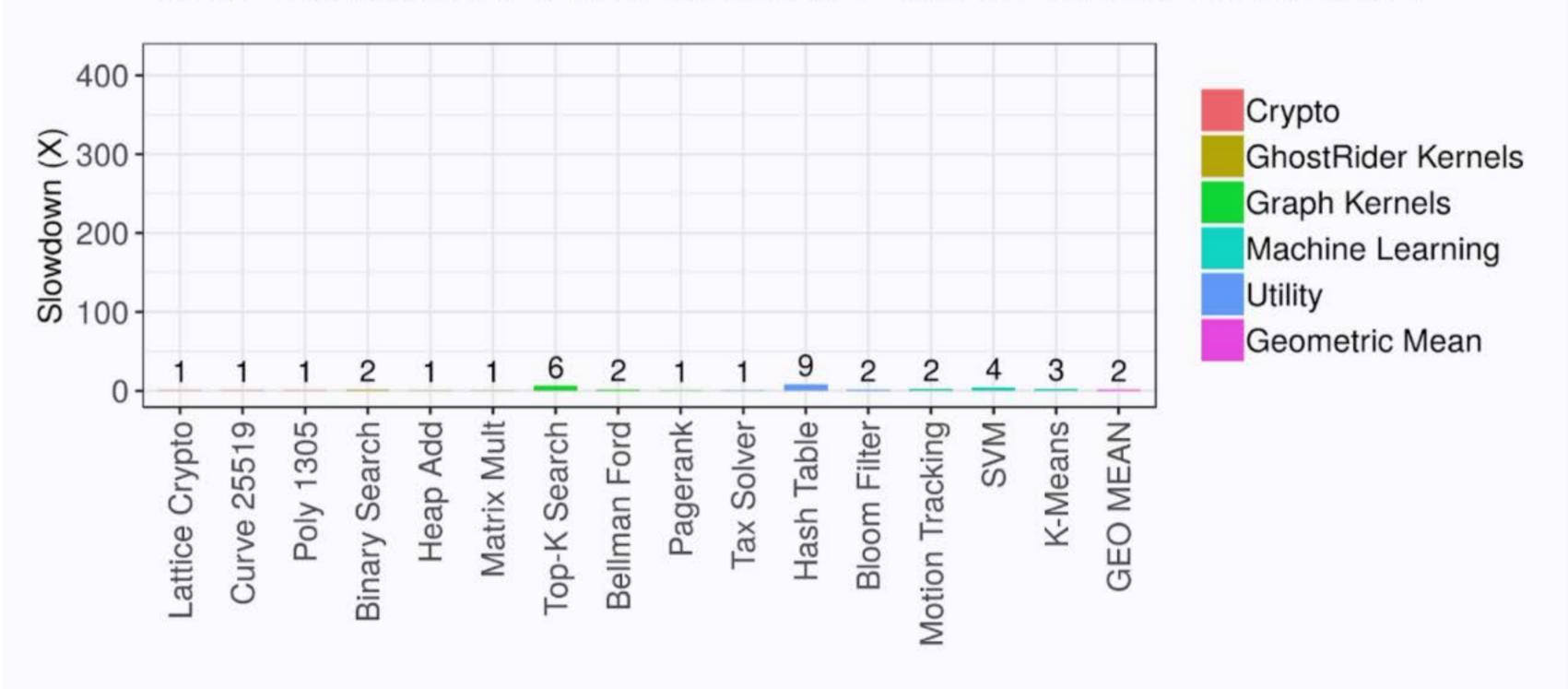

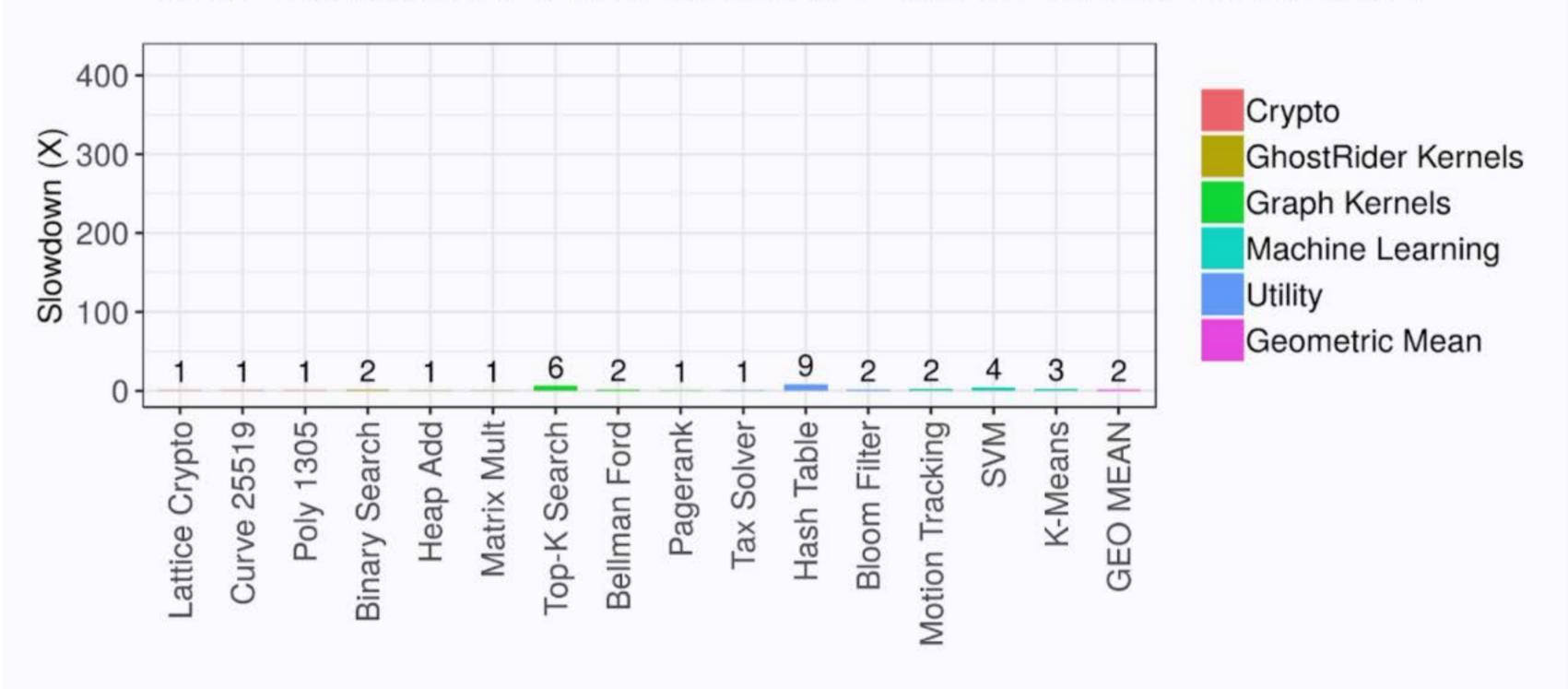

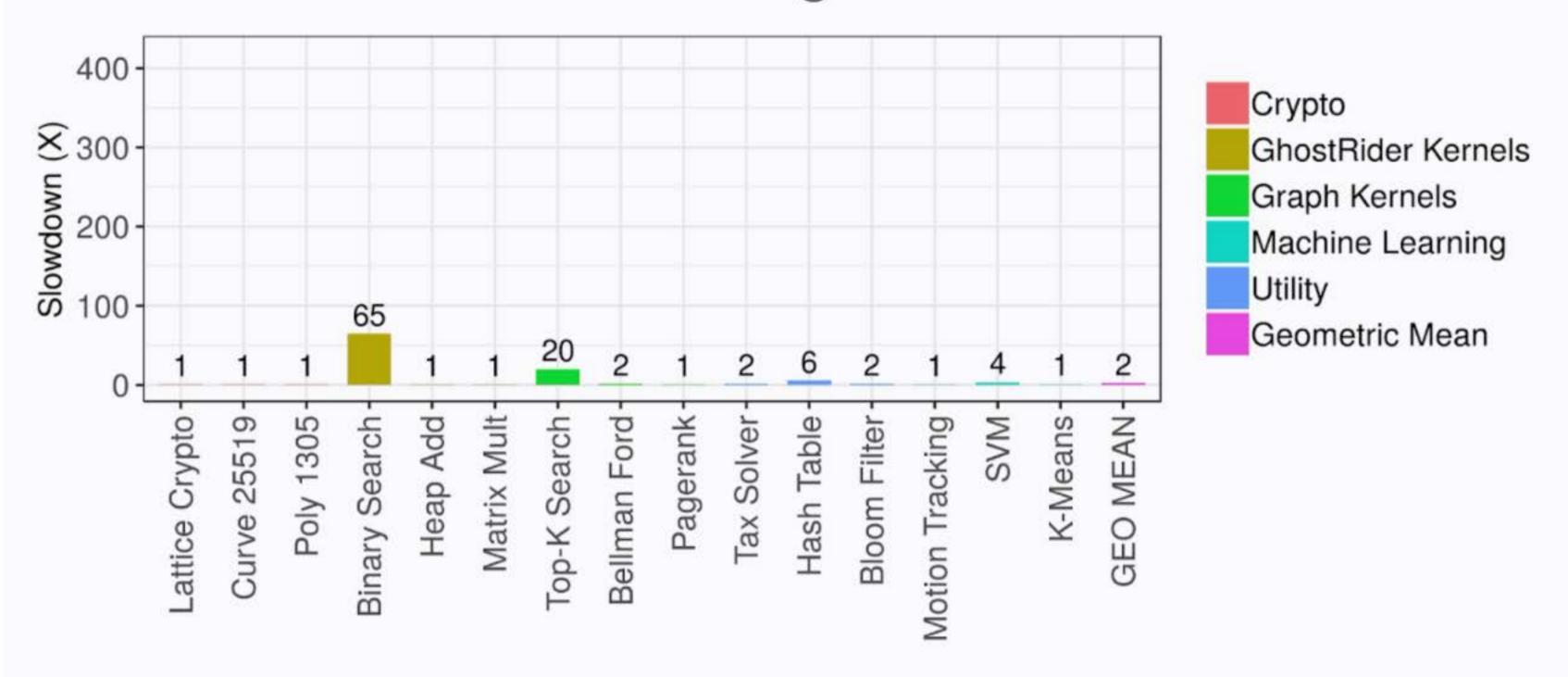

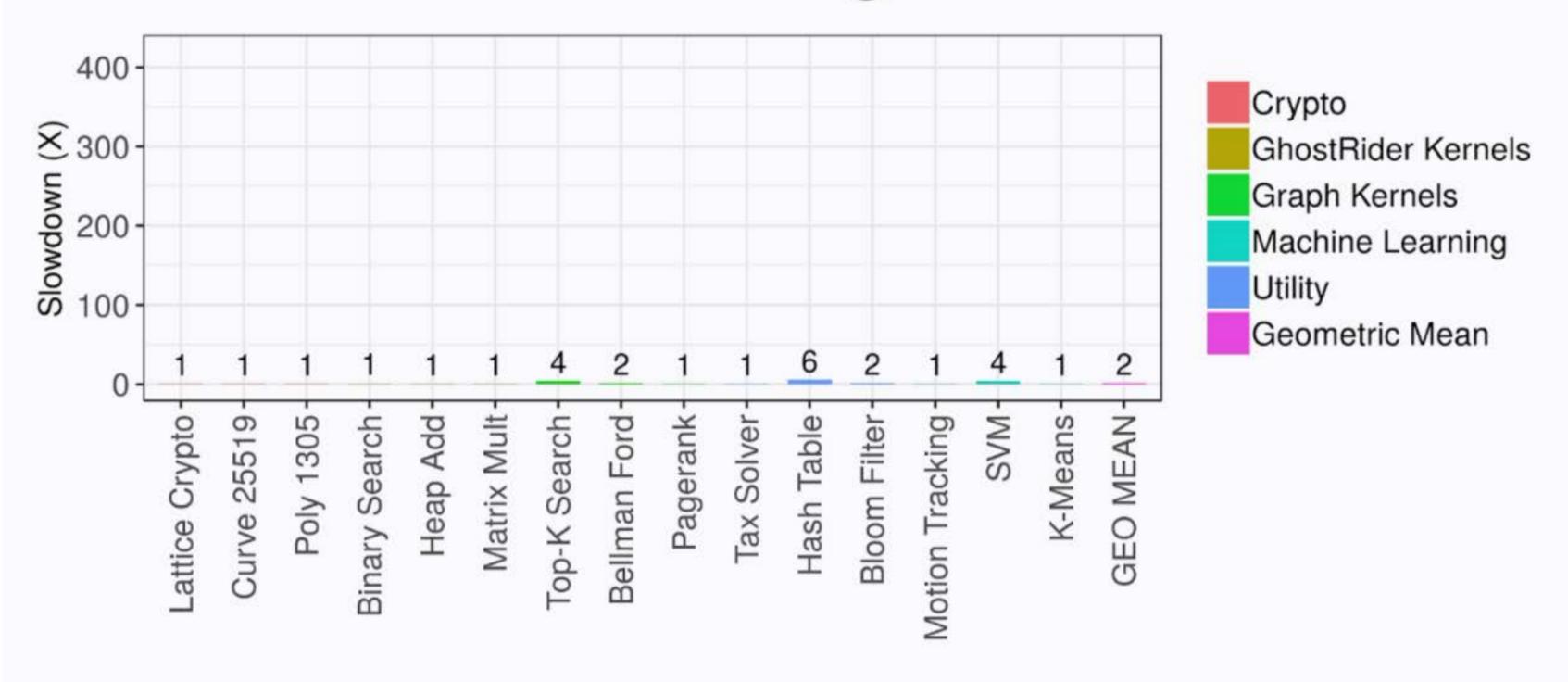

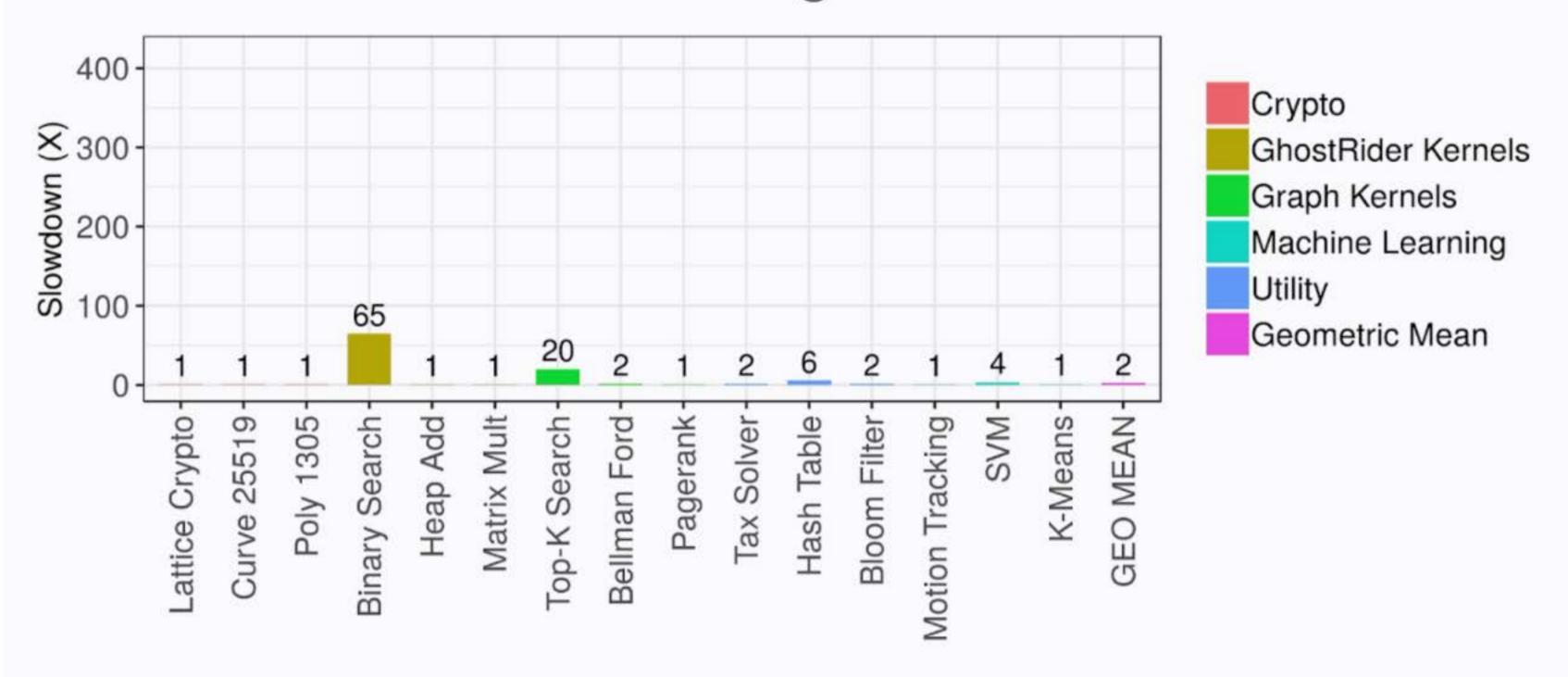

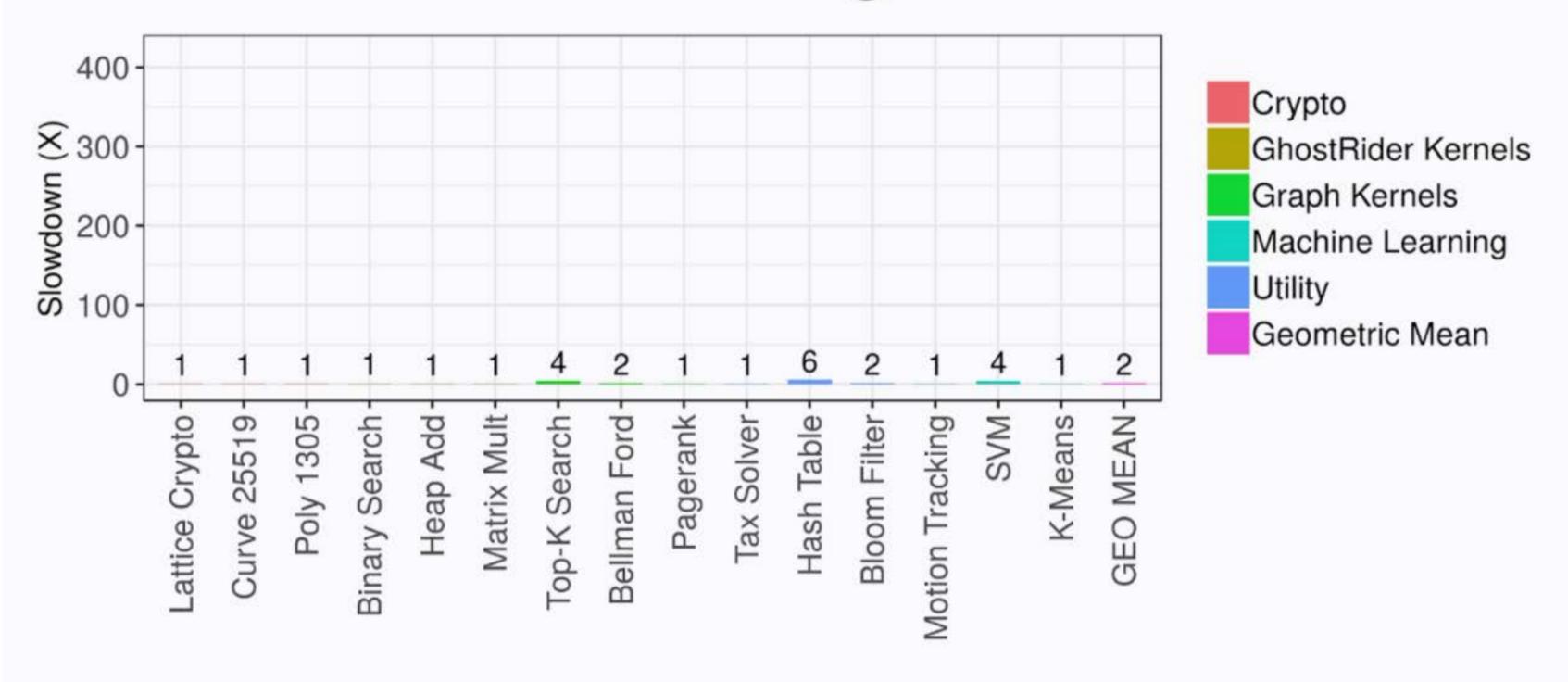

# Performance Impact of Using Point Solution

Disabled optimizations result in significant performance overhead

Are point solutions, since they focus on symptoms and not the root cause, and they may not compose well.

Are point solutions, since they focus on symptoms and not the root cause, and they may not compose well.

Many require redesigned hardware, since the solution is forced to disable optimizations in compiler and microarch.

Are point solutions, since they focus on symptoms and not the root cause, and they may not compose well.

Many require redesigned hardware, since the solution is forced to disable optimizations in compiler and microarch.

Many are inflexible because they cannot be tailored to the program or to portions of the program.

# My Solutions

Closes a Broad Class of Side Channels

# My Solutions

Closes a Broad Class of Side Channels

Executes on Modern Microprocessors

# My Solutions

Closes a Broad Class of Side Channels

Executes on Modern Microprocessors

Protects a Diverse Set of Applications

| Raccoon         | Escort          | Vale            | Vantage          |

|-----------------|-----------------|-----------------|------------------|

| USENIX Security | USENIX Security | USENIX Security | Work In Progress |

| Symposium 2015  | Symposium 2016  | Symposium 2017  |                  |

Raccoon

USENIX Security Symposium 2015 Escort

USENIX Security Symposium 2016 Vale

USENIX Security Symposium 2017 Vantage

Work In Progress

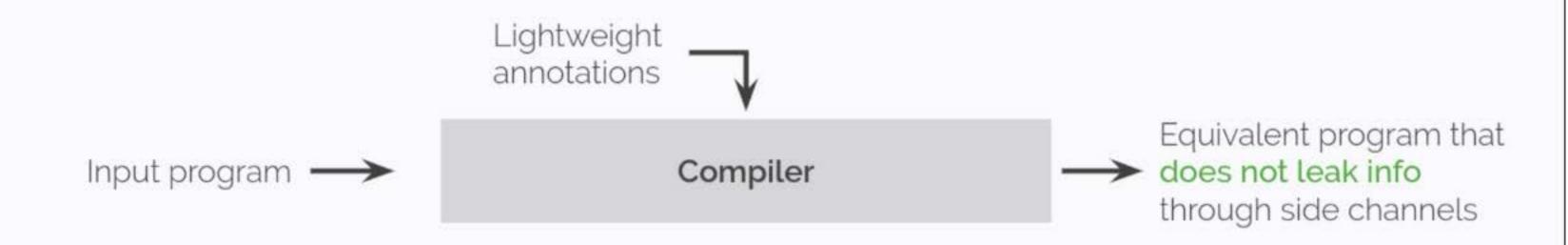

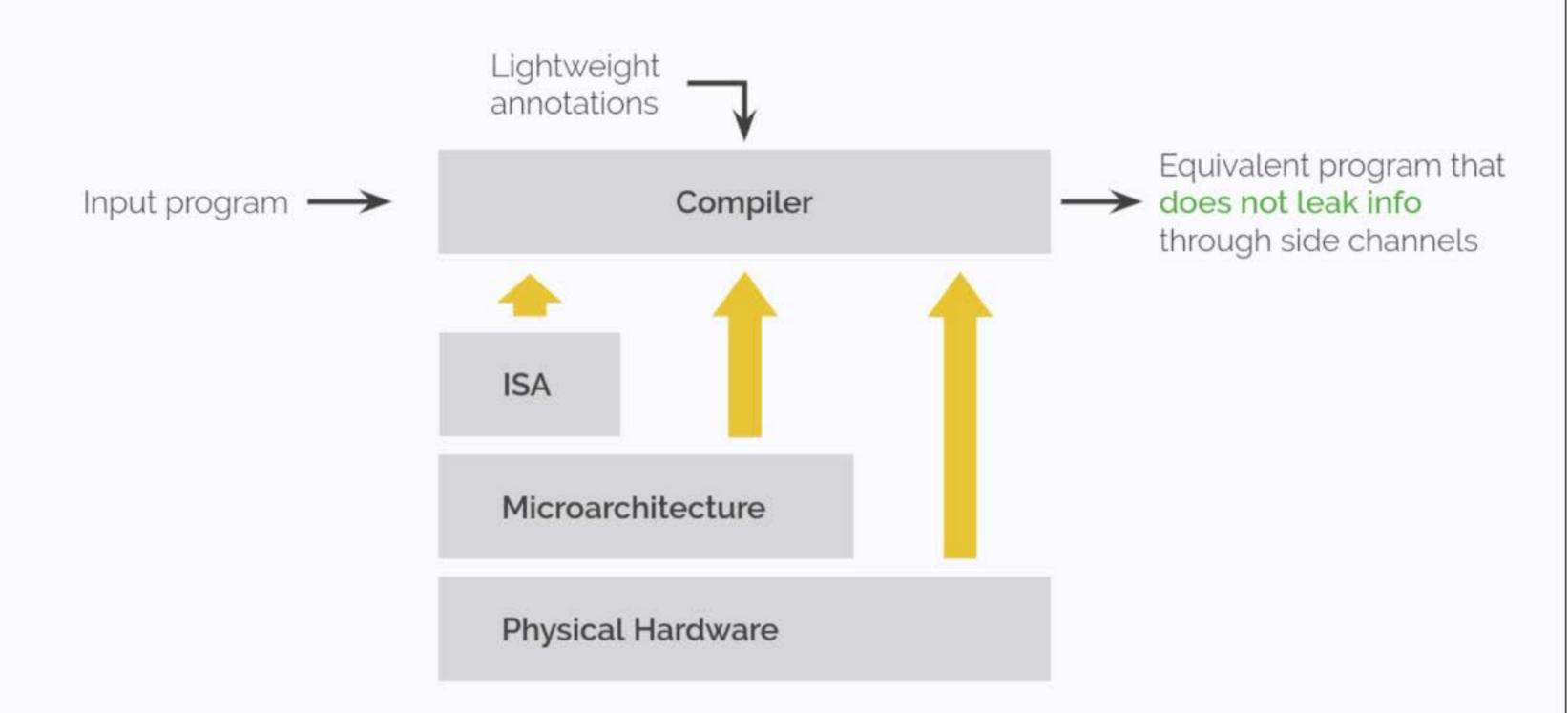

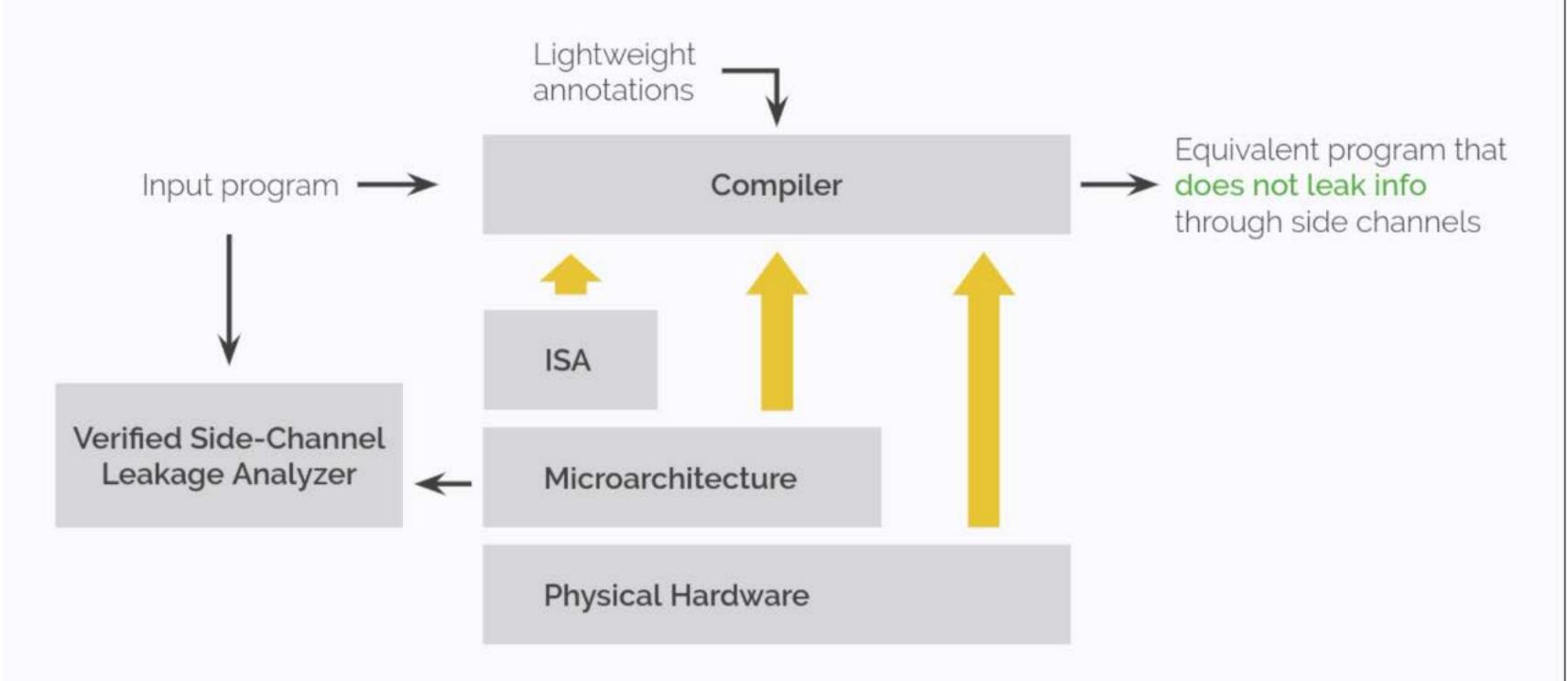

Compilers for closing all digital side channels

# RaccoonEscortValeVantageUSENIX Security<br/>Symposium 2015USENIX Security<br/>Symposium 2016USENIX Security<br/>Symposium 2017Work In Progress<br/>Symposium 2017

Compilers for closing all digital side channels

e.g. cache, address trace, branch predictor, TLB, etc.

Raccoon

USENIX Security Symposium 2015 Escort

USENIX Security Symposium 2016 Vale

USENIX Security Symposium 2017 Vantage

Work In Progress

Verified side channel leakage analyzer

Raccoon

USENIX Security Symposium 2015 Escort

USENIX Security Symposium 2016 Vale

USENIX Security Symposium 2017 Vantage

Work In Progress

Compiler that mitigates power side channel attacks in diverse programs and microarchitectures

Our Solution's Design

- Our Solution's Design

- Core Principles that Enable Generalization

- Our Solution's Design

- Core Principles that Enable Generalization

- > Performance Comparison

- Our Solution's Design

- Core Principles that Enable Generalization

- > Performance Comparison

- > Future Work

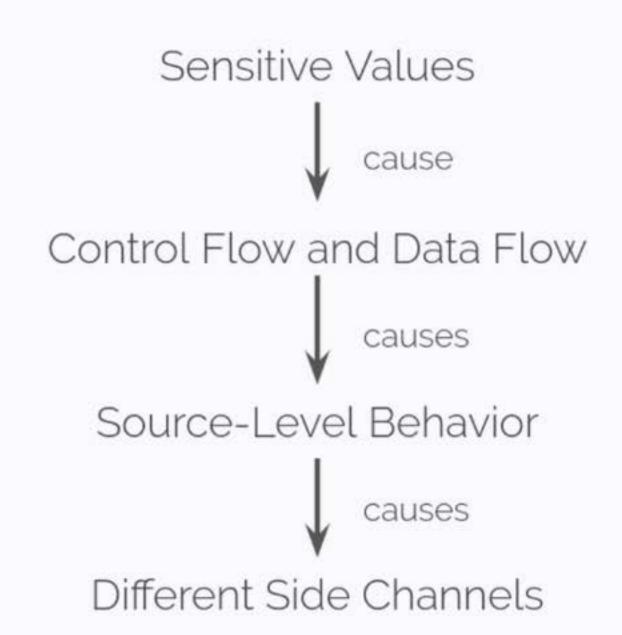

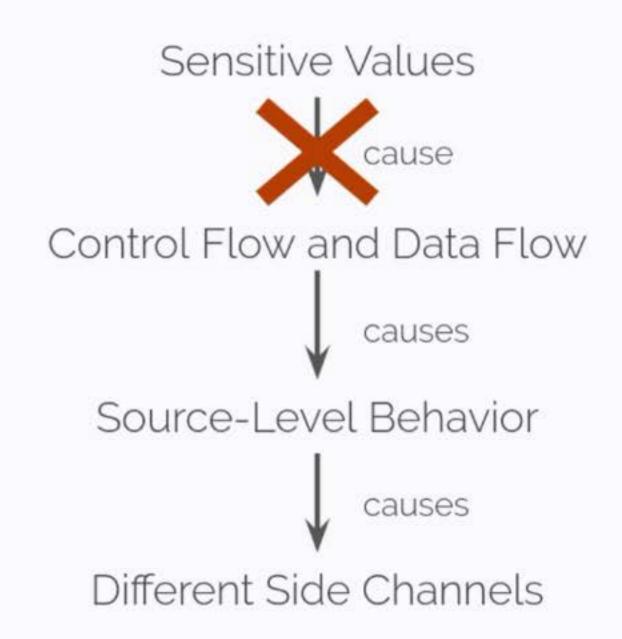

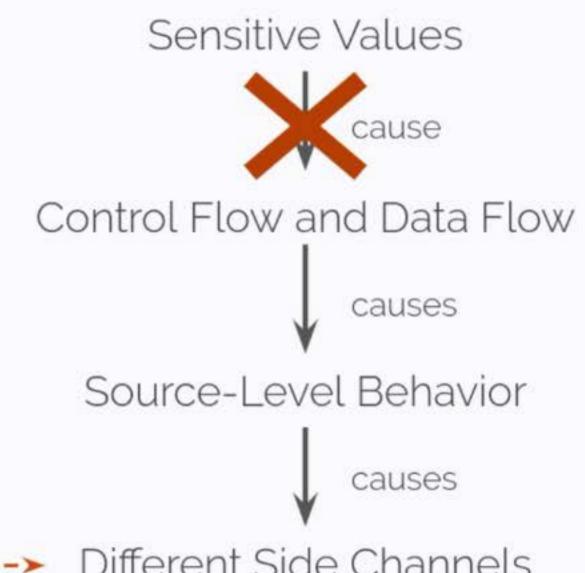

A broad range of side channels arise due to variations in source-level behavior.

A broad range of side channels arise due to variations in source-level behavior.

- Branch predictor side channel is caused by program path

- Memory trace channel is caused by pointer dereferences and program path

- Instruction count is caused by program path

Source-Level Behavior

causes

Different Side Channels

Control Flow and Data Flow

causes

Source-Level Behavior

causes

Different Side Channels

To close a broad class of side channels, make control flow and data flow independent of sensitive information.

To close a broad class of side channels, make control flow and data flow independent of sensitive information.

Point Solutions ---> Different Side Channels

## Solution: Execute All Paths

```

if (secret_bit == 1) {

z = (msg * z * z) mod n;

} else {

z = (z * z) mod n;

}

```

## Solution: Execute All Paths

Adversary sees secret\_bit = 1

## Solution: Execute All Paths

```

if (secret_bit == 1) {

z = (msg * z * z) mod n;

} else {

z = (z * z) mod n;

}

```

Adversary sees secret\_bit = 1

and secret\_bit != 1.

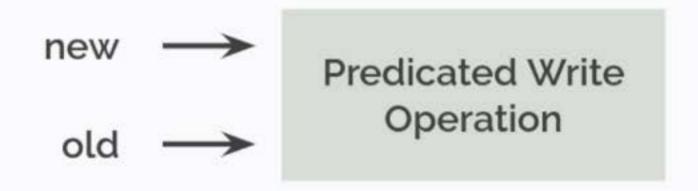

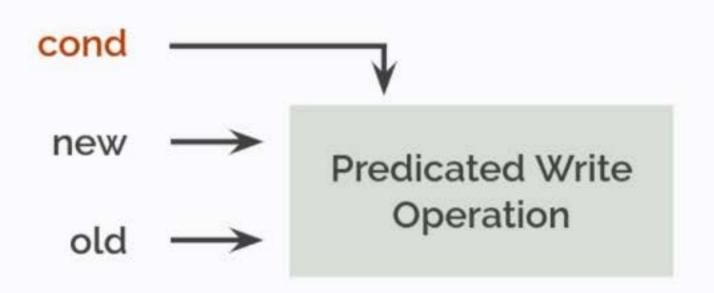

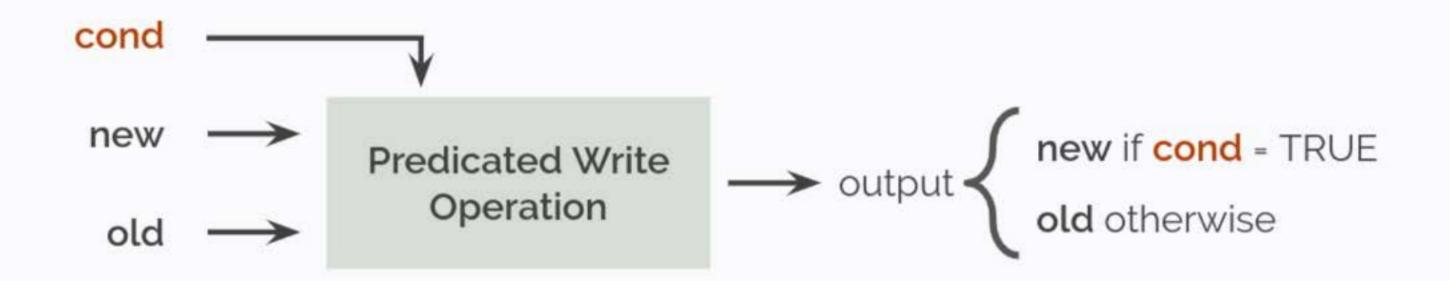

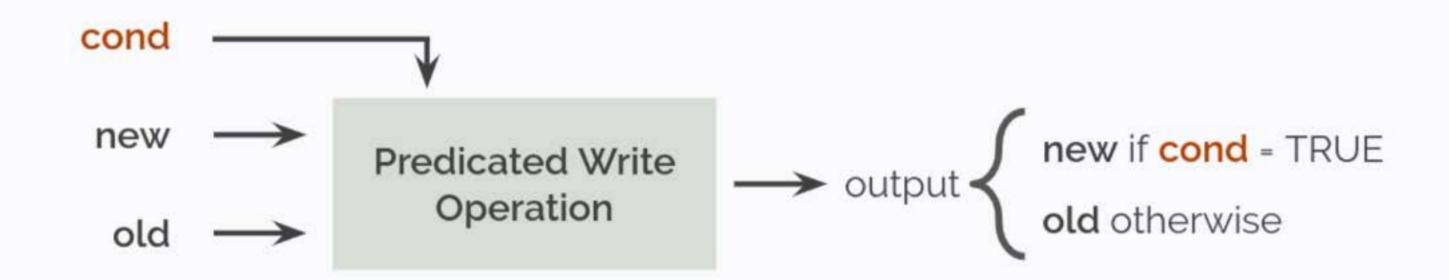

## **Predication** to Execute All Paths

### **Original** Program

```

if (secret_bit == 1) {

z = (msg * z * z) mod n;

} else {

z = (z * z) mod n;

}

```

## **Predication** to Execute All Paths

### **Original** Program

```

if (secret_bit == 1) {

z = (msg * z * z) mod n;

} else {

z = (z * z) mod n;

}

```

```

p = (secret_bit == 1)

p : z = (msg * z * z) mod n;

¬p: z = (z * z) mod n;

```

Implementation in x64 assembly:

```

mov old -> output  // Set destination

test cond, cond  // Check if non-zero

cmovz new -> output  // Conditional update

test 0, 0  // Overwrite flags

```

Also implemented using ARM v7, ARM v8, and RISC-V assembly instructions.

1. Straight-line control flow

- Straight-line control flow

- 2. All data in registers; no pointer dereferences

```

mov old -> output  // Set destination

test cond, cond  // Check if non-zero

cmovz new -> output  // Conditional update

test 0, 0  // Overwrite flags

```

- Straight-line control flow

- All data in registers;no pointer dereferences

- 3. Fixed execution time

```

mov old -> output  // Set destination

test cond, cond  // Check if non-zero

cmovz new -> output  // Conditional update

test 0, 0  // Overwrite flags

```

### **Original** Program

```

if (secret_bit == 1) {

z = (msg * z * z) mod n

} else {

z = (z * z) mod n

}

```

```

p = (secret_bit == 1)

z1 = (msg * z * z) mod n

z2 = (z * z) mod n

z = pred_write(p, z1, z)

z = pred_write(!p, z2, z)

```

### **Original** Program

```

if (secret_bit == 1) {

z = (msg * z * z) mod n

} else {

z = (z * z) mod n

}

```

```

p = (secret_bit == 1)

z1 = (msg * z * z) mod n

z2 = (z * z) mod n

z = pred_write(p, z1, z)

z = pred_write(!p, z2, z)

```

### **Original** Program

```

if (secret_bit == 1) {

z = (msg * z * z) mod n

} else {

z = (z * z) mod n

}

```

### **Transformed** Program

```

p = (secret_bit == 1)

z1 = (msg * z * z) mod n

z2 = (z * z) mod n

z = pred_write(p, z1, z)

```

z = pred\_write(!p, z2, z)

### **Original** Program

```

if (secret_bit == 1) {

z = (msg * z * z) mod n

} else {

z = (z * z) mod n

}

```

```

p = (secret_bit == 1)

z1 = (msg * z * z) mod n

z2 = (z * z) mod n

```

```

z = pred_write(p, z1, z)

z = pred_write(!p, z2, z)

```

### **Original** Program

```

if (secret_bit == 1) {

z = (msg * z * z) mod n

} else {

z = (z * z) mod n

}

```

```

p = (secret_bit == 1)

z1 = (msg * z * z) mod n

z2 = (z * z) mod n

z = pred_write(p, z1, z)

z = pred_write(!p, z2, z)

```

### Original Program

```

v = 0;

if (secret) {

v = 10;

y = x / v;

}

```

### Original Program

```

v = 0;

if (secret) {

v = 10;

y = x / v;

}

```

```

v = 0;

v = pred_write(secret, 10, v);

y = pred_write(secret, x/v, y);

```

### Original Program

```

v = 0;

if (secret) {

v = 10;

y = x / v;

}

```

```

v = 0;

v = pred_write(secret, 10, v);

y = pred_write(secret, x/v, y);

```

### Original Program

```

v = 0;

if (secret) {

v = 10;

y = x / v;

}

```

### **Transformed** Program

```

v = 0;

v = pred_write(secret, 10, v);

y = pred_write(secret, x/v, y);

```

If secret is false, v is not updated, hence v remains o.

### **Original** Program

```

v = 0;

if (secret) {

v = 10;

y = x / v;

}

```

### **Transformed** Program

```

v = 0;

v = pred_write(secret, 10, v);

y = pred_write(secret, x/v y);

```

If secret is false, v is not updated, hence v remains o.

Division by zero exception causes program to terminate.

### Original Program

```

v = 0;

if (secret) {

v = 10;

y = x / v;

}

```

```

v = 0;

v = pred_write(secret, 10, v);

y = pred_write(secret, x/v, y);

```

```

v = 0;

v = pred_write(secret, 10, v);

t = pred_write(v == 0, 1, v);

y = pred_write(secret, x/t, y);

```

### **Original** Program

```

v = 0;

if (secret) {

v = 10;

y = x / v;

}

```

Our solution masks exceptions by covertly changing divisor value.

```

v = 0;

v = pred_write(secret, 10, v);

y = pred_write(secret, x/v, y);

```

```

v = 0;

v = pred_write(secret, 10, v);

t = pred_write(v == 0, 1, v);

y = pred_write(secret, x/t, y);

```

### Original Program

```

v = 0;

if (secret) {

v = 10;

y = x / v;

}

```

```

v = 0;

v = pred_write(secret, 10, v);

y = pred_write(secret, x/v, y);

```

```

v = 0;

v = pred_write(secret, 10, v);

t = pred_write(v == 0, 1, v);

y = pred_write(secret, x/t, y);

```

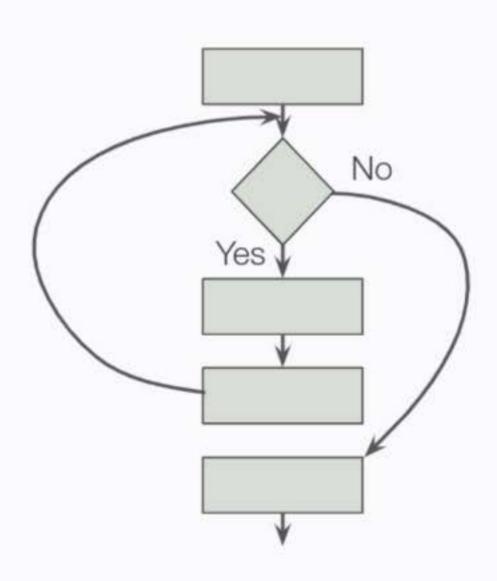

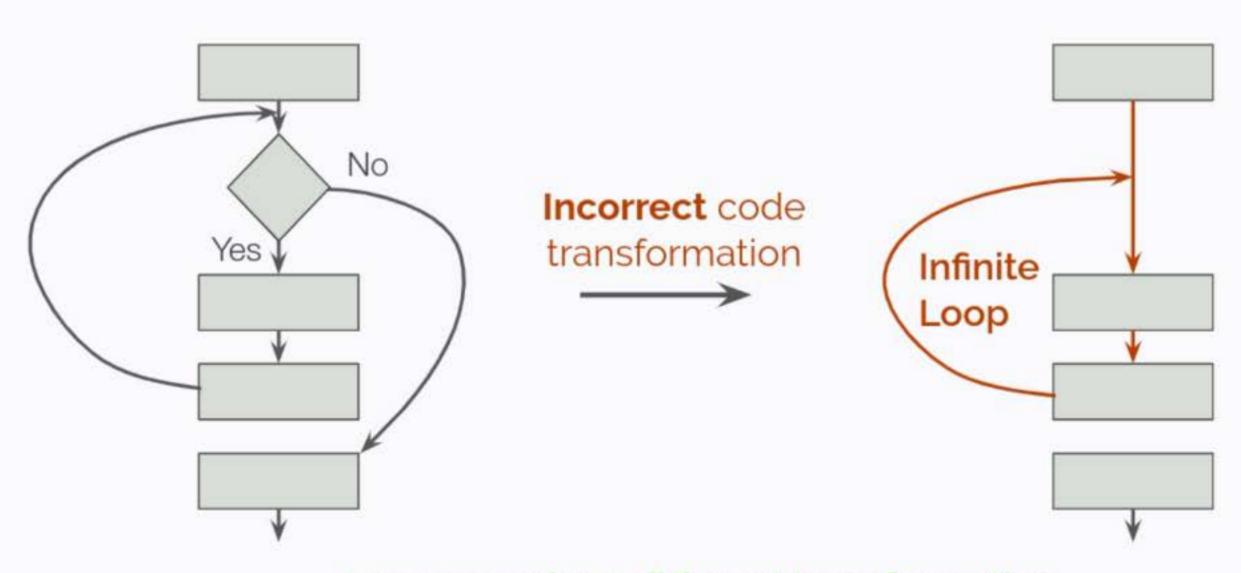

# But Predication May Cause Infinite Loops

# But Predication May Cause Infinite Loops

# But Predication May Cause Infinite Loops

Loops require a different transformation.

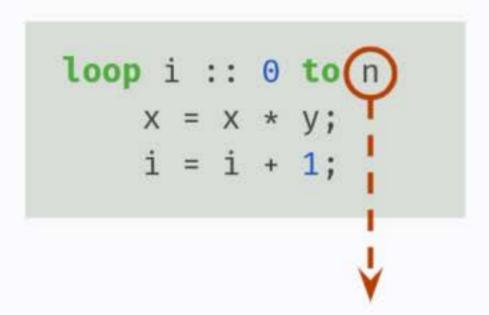

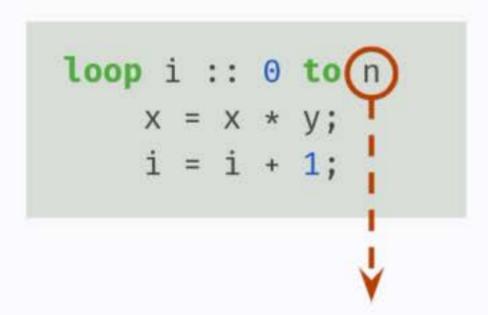

# Transforming Loops

```

loop i :: 0 to n

x = x * y;

i = i + 1;

```

# Transforming Loops

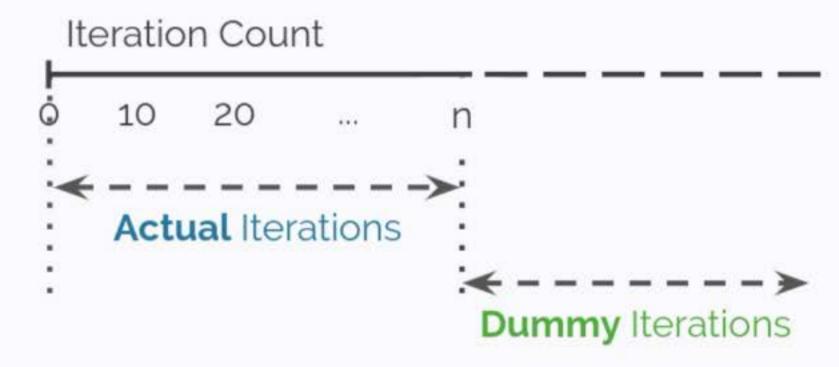

#### Assume n is secret.

Transformation should hide the number of executed iterations.

# Transforming Loops

#### Assume n is secret.

Transformation should hide the number of executed iterations.

## Our Solution's Approach

### Original Program

```

loop i :: 0 to n

x = x * y;

i = i + 1;

```

### Original Program

```

loop i :: 0 to n

x = x * y;

i = i + 1;

```

### **Transformed** Program

```

i = 0

loop ctr :: 0 to C

```

ctr = ctr + 1;

### Original Program **Transformed** Program i = 0loop i :: 0 to n X = X \* y;loop ctr :: 0 to C i = i + 1;New predicate - - p: x = x \* y; for loop body p: i = i + 1; for loop body ctr = ctr + 1;

#### **Original** Program

```

loop i :: 0 to n

x = x * y;

i = i + 1;

```

#### **Transformed** Program

```

i = 0

p = TRUE

loop ctr :: 0 to C

p: x = x * y;

p: i = i + 1;

ctr = ctr + 1;

```

#### **Original** Program

```

loop i :: 0 to n

x = x * y;

i = i + 1;

```

### **Transformed** Program

#### Original Program

```

loop i :: 0 to n

x = x * y;

i = i + 1;

```

Annotated by user, for example: <-\_\_loop\_count(1024)

#### **Transformed** Program

```

i = 0

p = TRUE

loop ctr :: 0 to C

p: x = x * y;

p: i = i + 1;

i == n: p = FALSE;

ctr = ctr + 1;

```

# Variations In Program Behavior

Control Flow

Data Flow

### Variations in **Data Flow**

```

result = table[secret];

```

### Variations in **Data Flow**

### Variations in **Data Flow**

### Eliminating Variations in **Data Flow**

#### Solution #1: Array Streaming

Accesses the entire array to read one element of the array.

Expensive to access entire array, but vector instructions, caches, and prefetchers reduce latency.

### Eliminating Variations in Data Flow

#### Solution #1: Array Streaming

Accesses the entire array to read one element of the array.

Expensive to access entire array, but vector instructions, caches, and prefetchers reduce latency.

#### Solution #2: Software ORAM

Software version of Path ORAM [CCS'13], which shuffles memory to hide location of data.

# Variations In Program Behavior

Control Flow

Data Flow

# Variations In Program Behavior

Control Flow

Data Flow

ISA Instructions

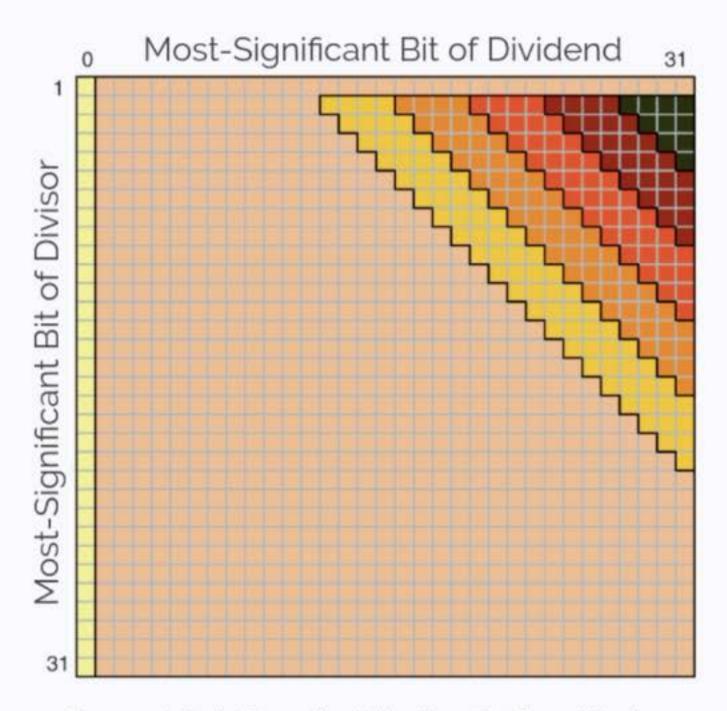

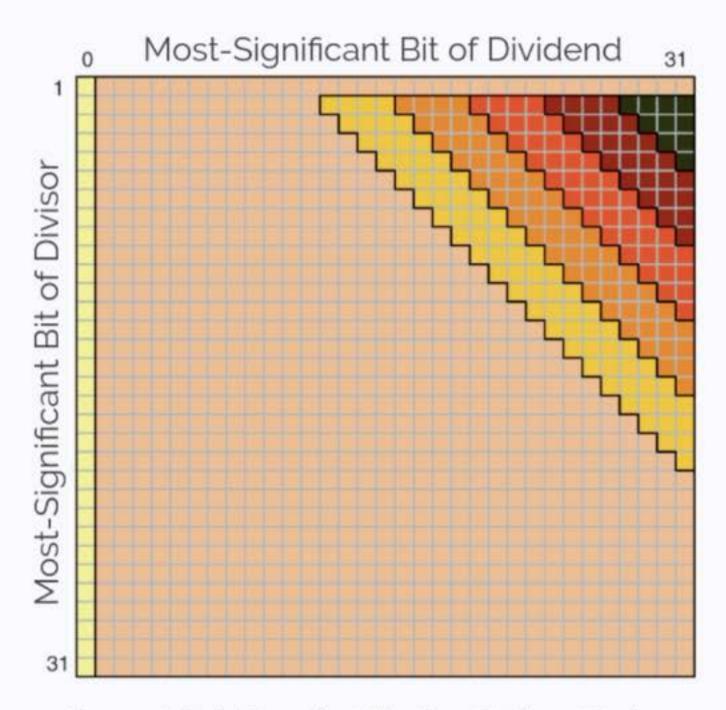

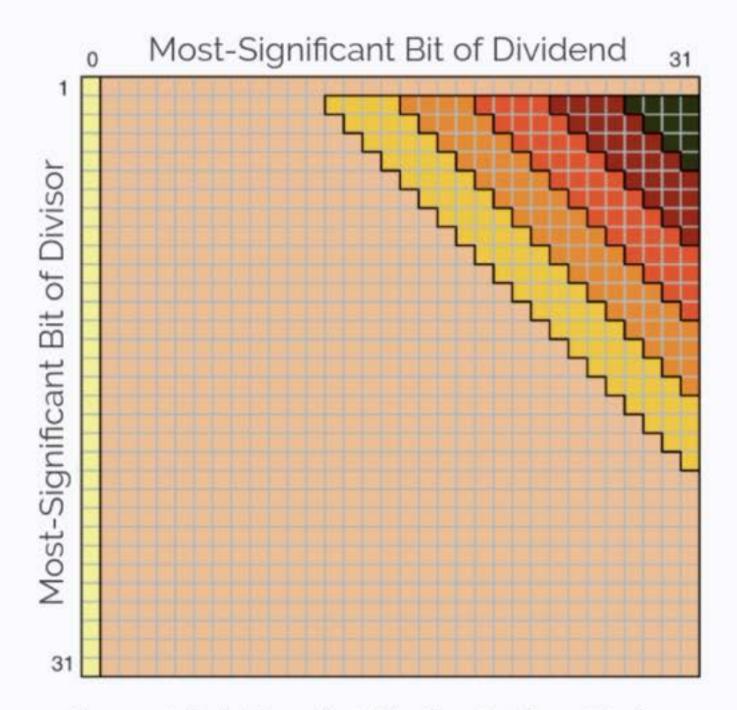

Cleemput et al., "Compiler Mitigations for Time Attacks on Modern x86 Processors", ACM TACO 2012.

Cleemput et al., "Compiler Mitigations for Time Attacks on Modern x86 Processors", ACM TACO 2012.

Colors indicate different execution times

Colors indicate different execution times

Execution time depends on the operand values, creating timing side channel

Cleemput et al., "Compiler Mitigations for Time Attacks on Modern x86 Processors", ACM TACO 2012.

Cleemput et al., "Compiler Mitigations for Time Attacks on Modern x86 Processors", ACM TACO 2012.

Colors indicate different execution times

Execution time depends on the operand values, creating timing side channel

**Solution:** Rewrite division using bitwise arithmetic

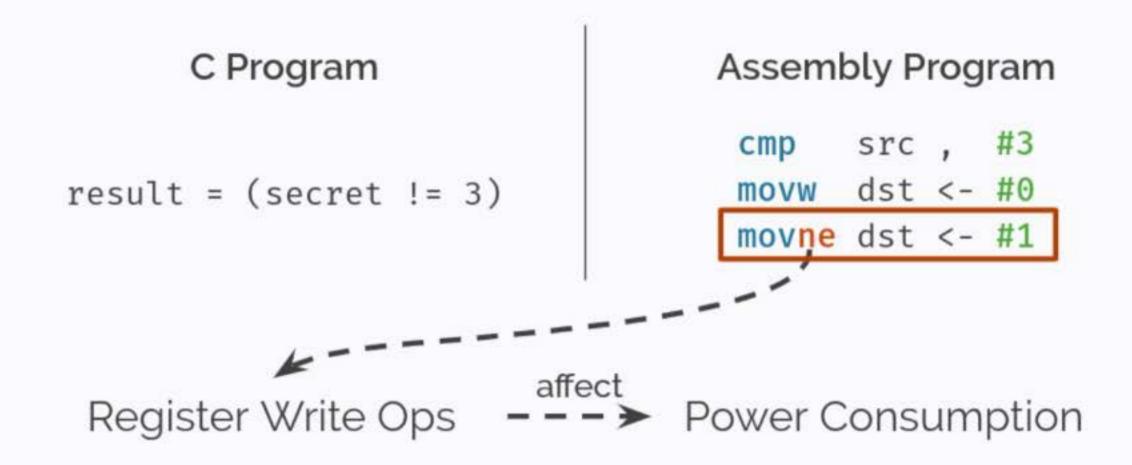

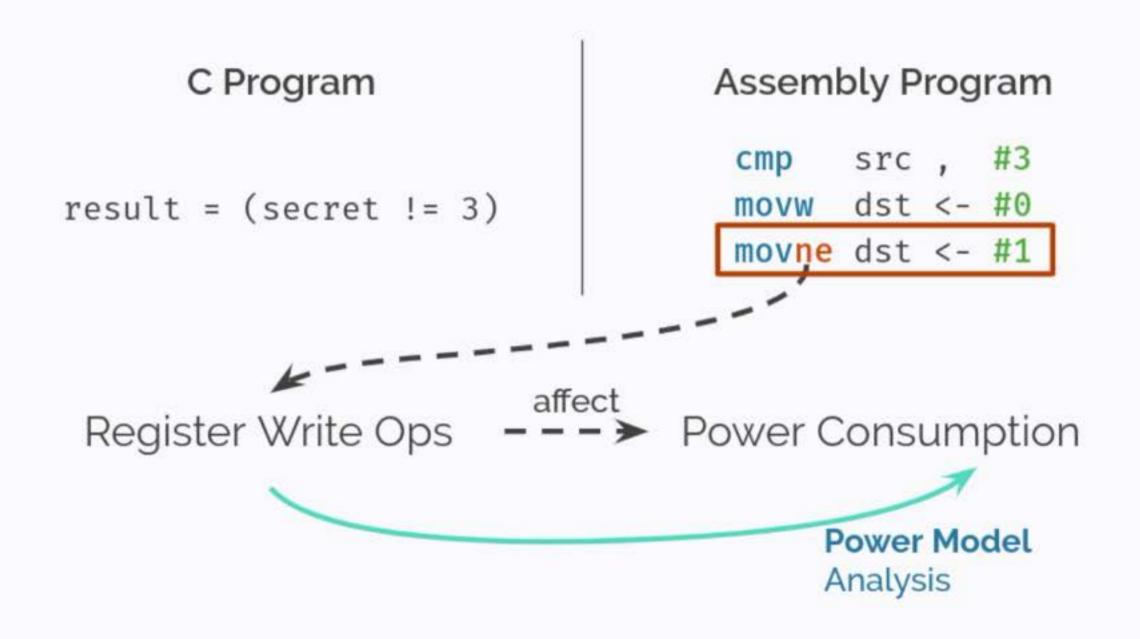

### C Program

```

result = (secret != 3)

```

#### **Assembly Program**

```

cmp src , #3

movw dst <- #0

movne dst <- #1</pre>

```

#### C Program

result = (secret != 3)

#### **Assembly Program**

```

cmp src , #3

movw dst <- #0

movne dst <- #1</pre>

```

Compares secret with the literal constant 3

### C Program

```

result = (secret != 3)

```

#### **Assembly Program**

```

cmp src , #3

movw dst <- #0

movne dst <- #1</pre>

```

Preemptively copies literal 0 into the destination

### C Program

```

result = (secret != 3)

```

#### **Assembly Program**

```

cmp src , #3

movw dst <- #0

movne dst <- #1</pre>

```

Conditionally copies literal 1 into the destination

### C Program

```

result = (secret != 3)

```

#### **Assembly Program**

```

cmp src , #3

movw dst <- #0

movne dst <- #1</pre>

```

Open Source Power Model

for example, McPAT

Open Source Power Model

for example, McPAT

We apply backward slicing to identify the microarchitectural metrics that affect dynamic power consumption.

Open Source Power Model

for example, McPAT

We apply backward slicing to identify the microarchitectural metrics that affect dynamic power consumption.

Closed Source Power Model

for example, Intel RAPL

Open Source Power Model

for example, McPAT

We apply backward slicing to identify the microarchitectural metrics that affect dynamic power consumption.

Closed Source Power Model

for example, Intel RAPL

We fit a **regression model** to the RAPL power model, and we identify the inputs that have non-zero regression coefficients.

## Superoptimizers for Alternate Code Sequences

### Original Assembly Program

```

cmp src1,src2

movw dst <- #0

movne dst <- #1</pre>

```

### Transformed Assembly Program

```

sub

tmp <- src1, src2</th>

sub

dst <- src2, src1</th>

orr

dst <- dst , tmp</th>

lsr

dst <- dst , #31</th>

```

### Outline

- Our Solution's Design

- Core Principles that Enable Generalization

- > Performance Comparison

- > Future Work

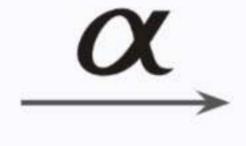

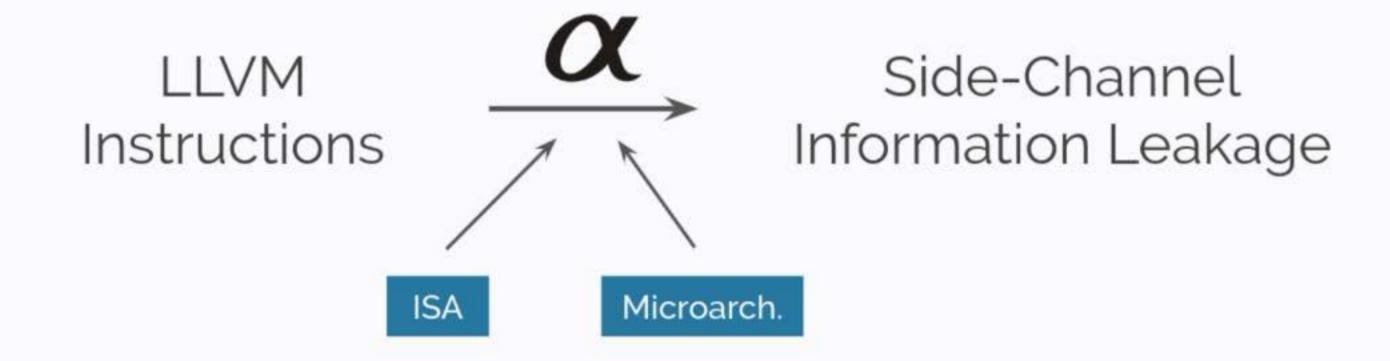

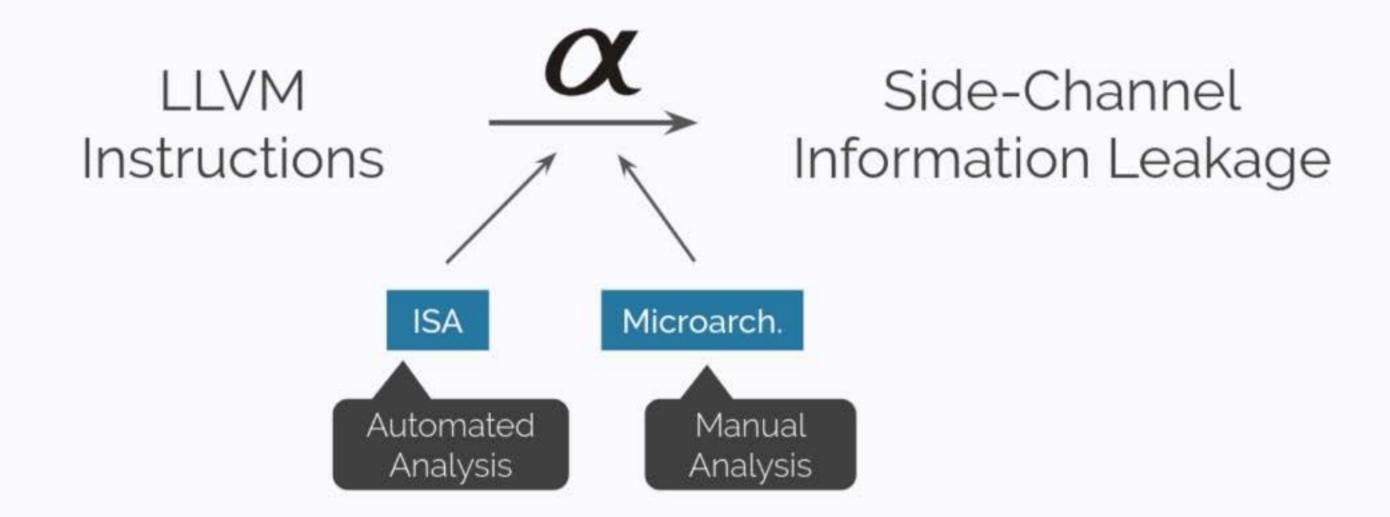

LLVM Instructions Side-Channel Information Leakage

LLVM Instructions Side-Channel Information Leakage

div numerator denominator

numerator denominator

LLVM Instructions

Side-Channel Information Leakage

div numerator denominator

numerator denominator

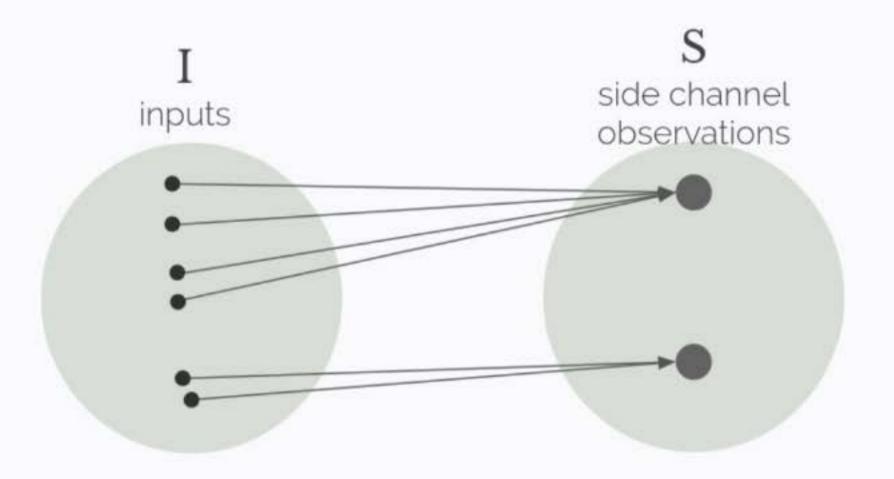

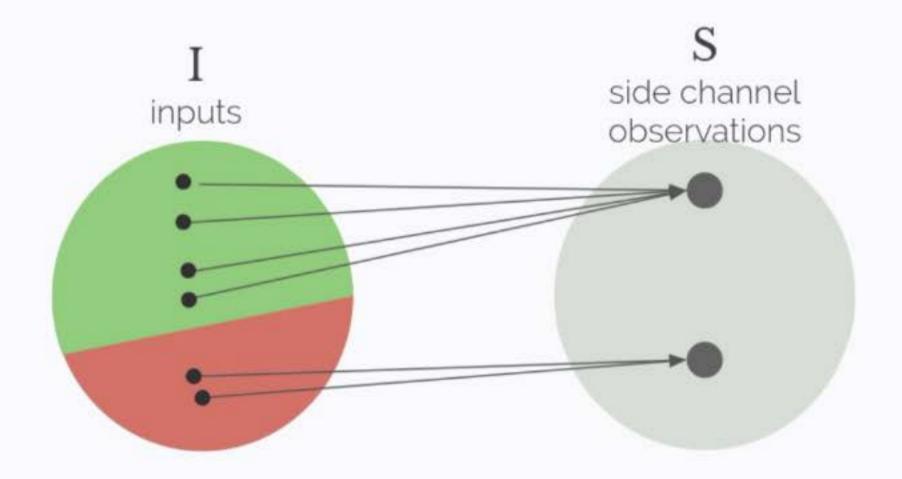

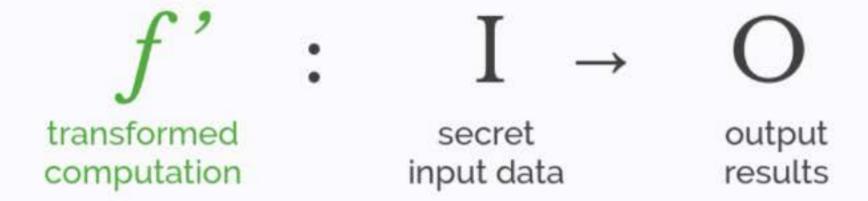

$f: I \to O$  computation secret output input data results

9

information leakage  $I \rightarrow$

secret input data S

side channel observations

information leakage secret input data

side channel observations

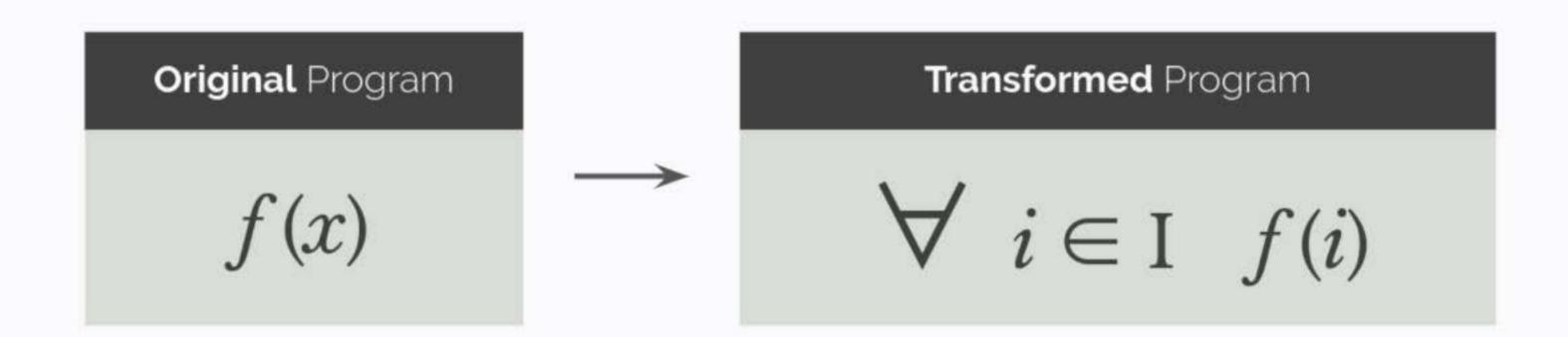

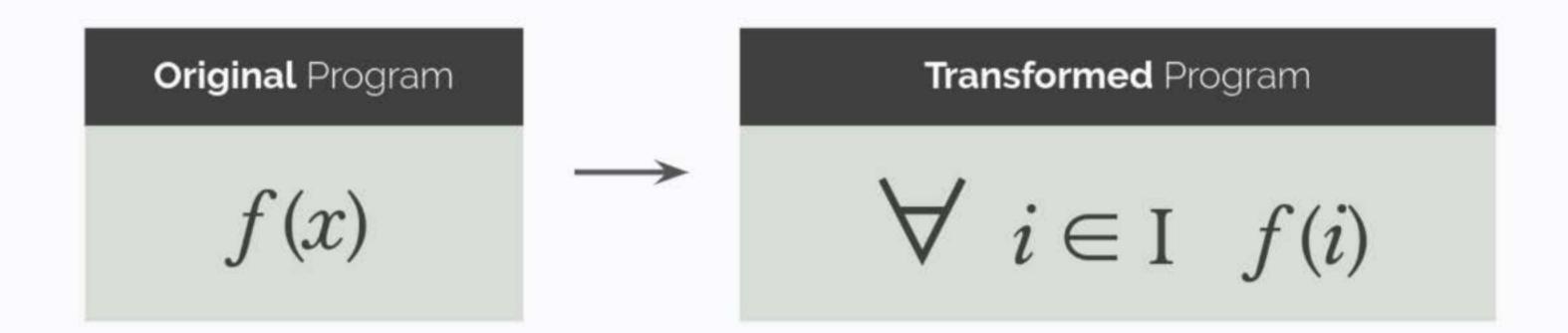

### Original Program

f(x)

# Initial Approach to Close Side Channel

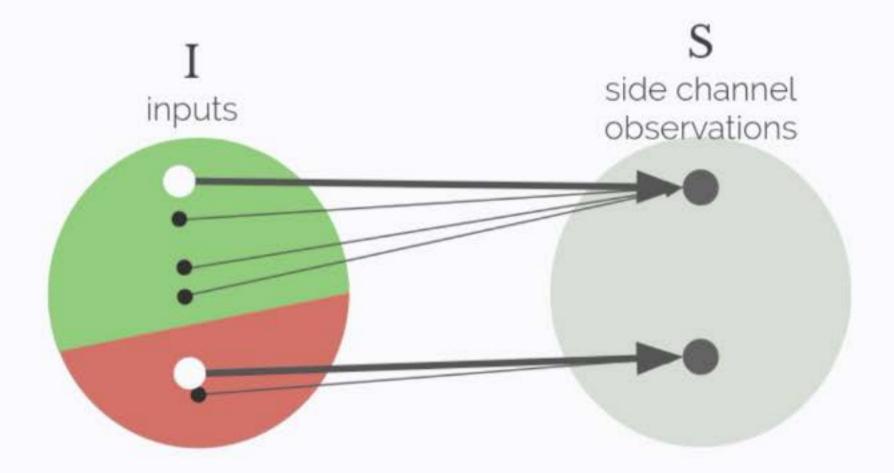

## Initial Approach to Close Side Channel

### Initial Approach to Close Side Channel

Inefficient if set of all possible inputs is large.

Use one representative input from each partition.

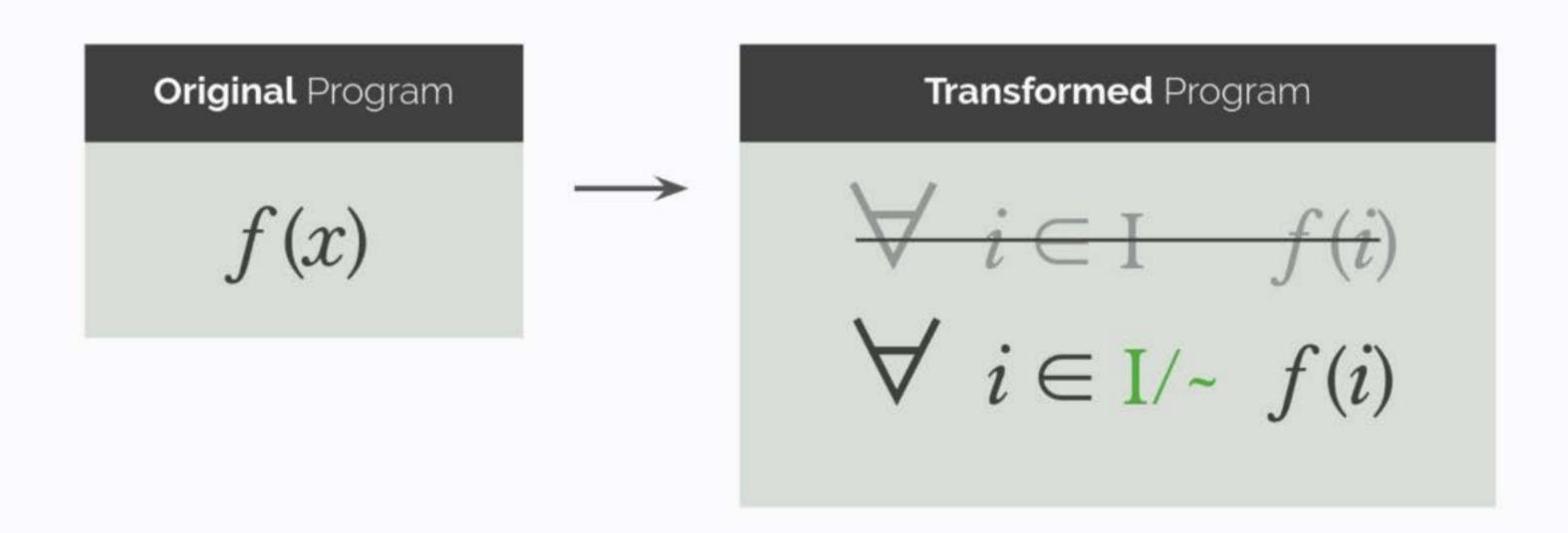

# Approach #3: Further Optimization

$$f: I \rightarrow O, l: I \rightarrow S$$

# Approach #3: Further Optimization

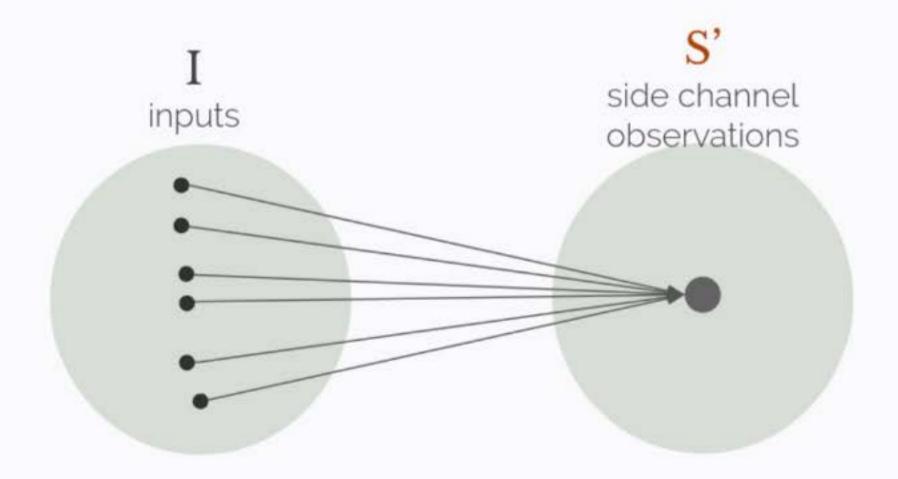

$$f: I \rightarrow O,$$

$l: I \rightarrow S$   $f': I \rightarrow O,$   $l': I \rightarrow S'$  with  $|S'| = 1$

# Approach #3: Further Optimization

$$f': I \rightarrow O,$$

$$f': I \rightarrow O,$$

$l': I \rightarrow S'$  with  $|S'| = 1$

#### **Original** Program

#### **Transformed** Program

$$\frac{\forall i \in I \quad f(i)}{\forall i \in I/\sim f(i)}$$

$$f'(x)$$

Close a Broad Class of Side Channels

Execute on Modern Microprocessors Protect a Diverse Set of Applications

Digital Side Channels

e.g. address trace, cache, branch predictor, etc.

Close a Broad Class of Side Channels

Execute on Moderr Microprocessors Protect a Diverse Set of Applications

**Digital** Side Channels and some **Non-Digital** Side Channels

e.g. instruction-level power consumption

Close a Broad Class of Side Channels

Execute on Modern Microprocessors Protect a Diverse Set of Applications

Microarchitectural Implementations of x64, 32-bit ARM, and 64-bit ARM ISAs

Close a Broad Class of Side Channels

Execute on Modern

Microprocessors

Protect a Diverse Set of Applications

Not just Cryptographic Implementations, but also Graph Kernels, Machine-Learning Libraries, etc.

### Outline

- Our Solution's Design

- Core Principles that Enable Generalization

- Performance Comparison

- > Future Work

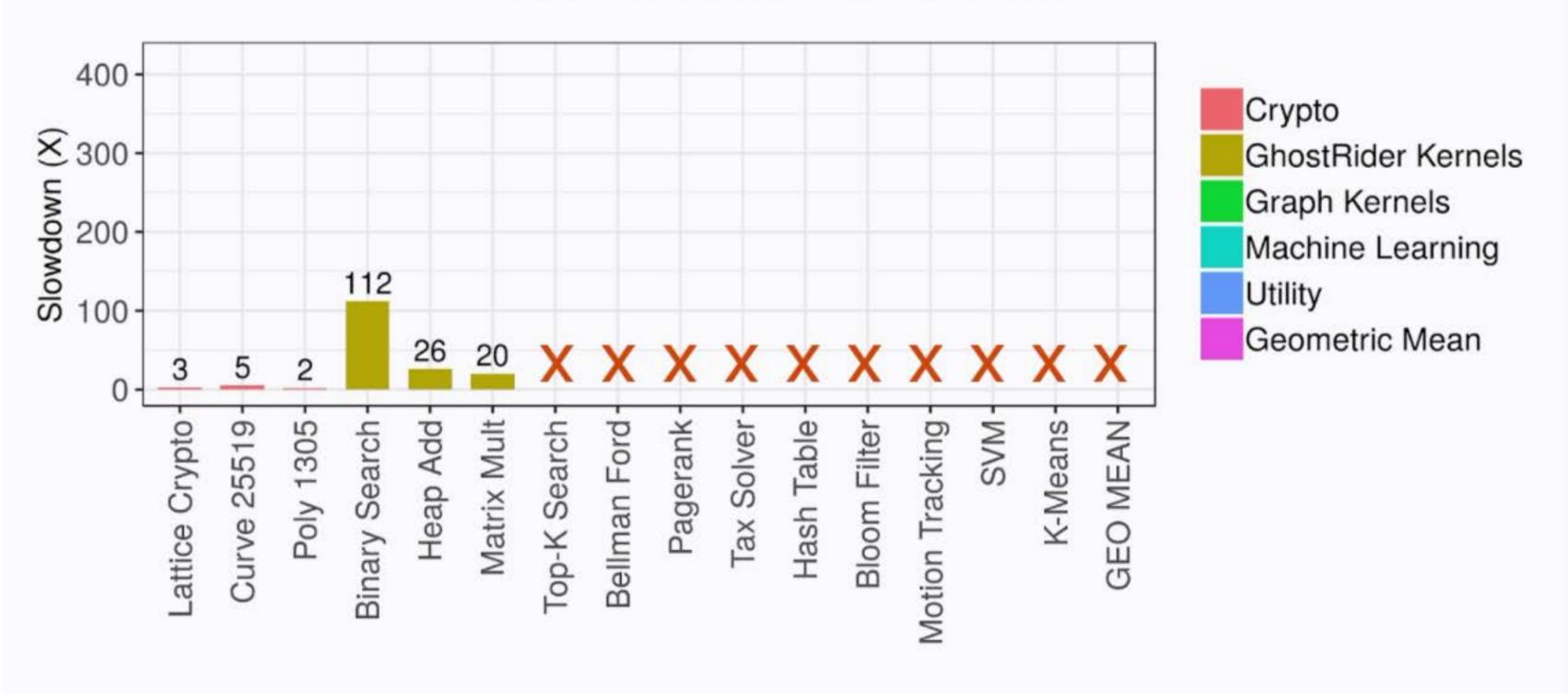

# Comparison With GhostRider

## **Evaluation** Programs

#### Cryptography

- Lattice Crypto

- Curve-25519

- Poly-1305

#### GhostRider

- Binary Search

- Heap Add

- Matrix Mult

#### **Graph Kernels**

- Top-K Search

- Bellman Ford

- PageRank

#### Machine Learning

- Motion Tracking

- SVM Classifier

#### **Utility Programs**

- Font Renderer

- Hash Table

- Bloom Filter

### **GhostRider** Evaluation

## Hardware-Only Solution Evaluation

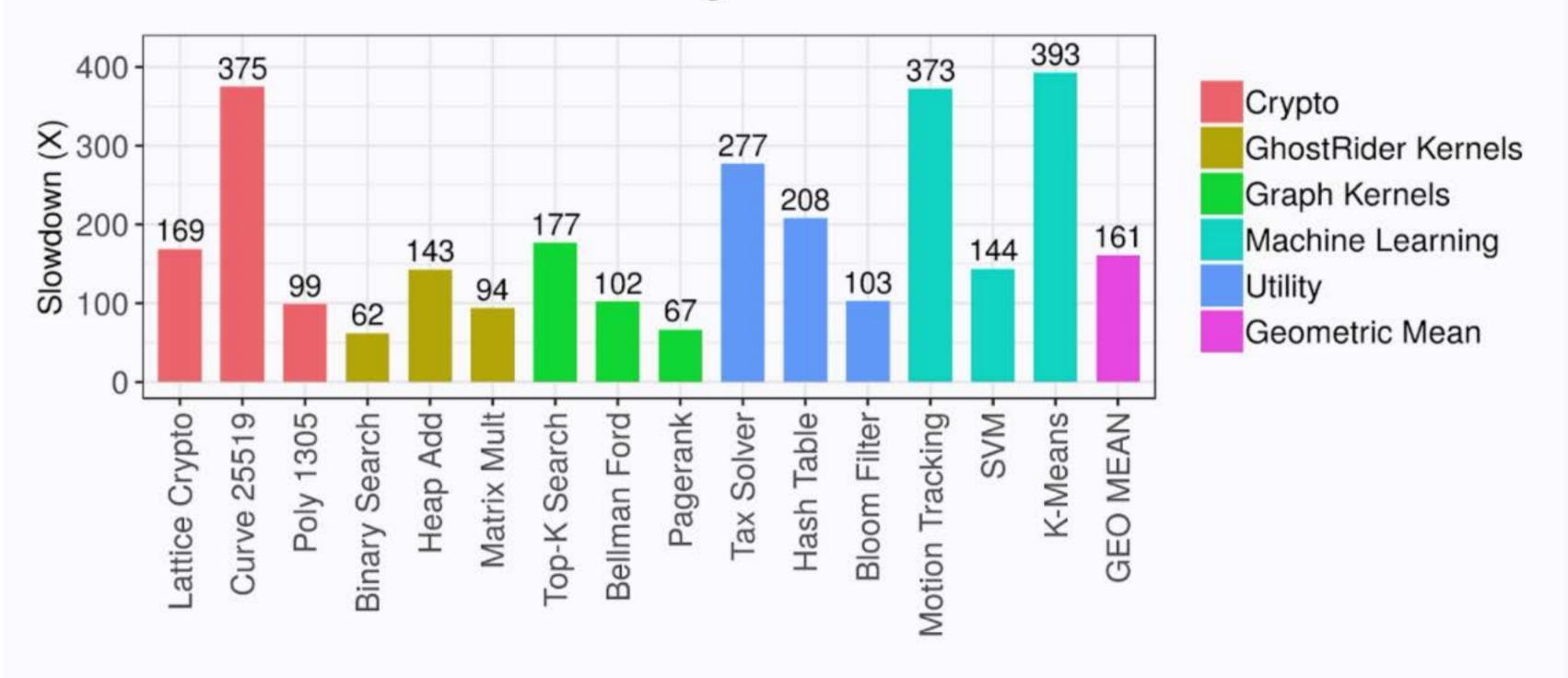

## Our Solution: All Digital Side Channels

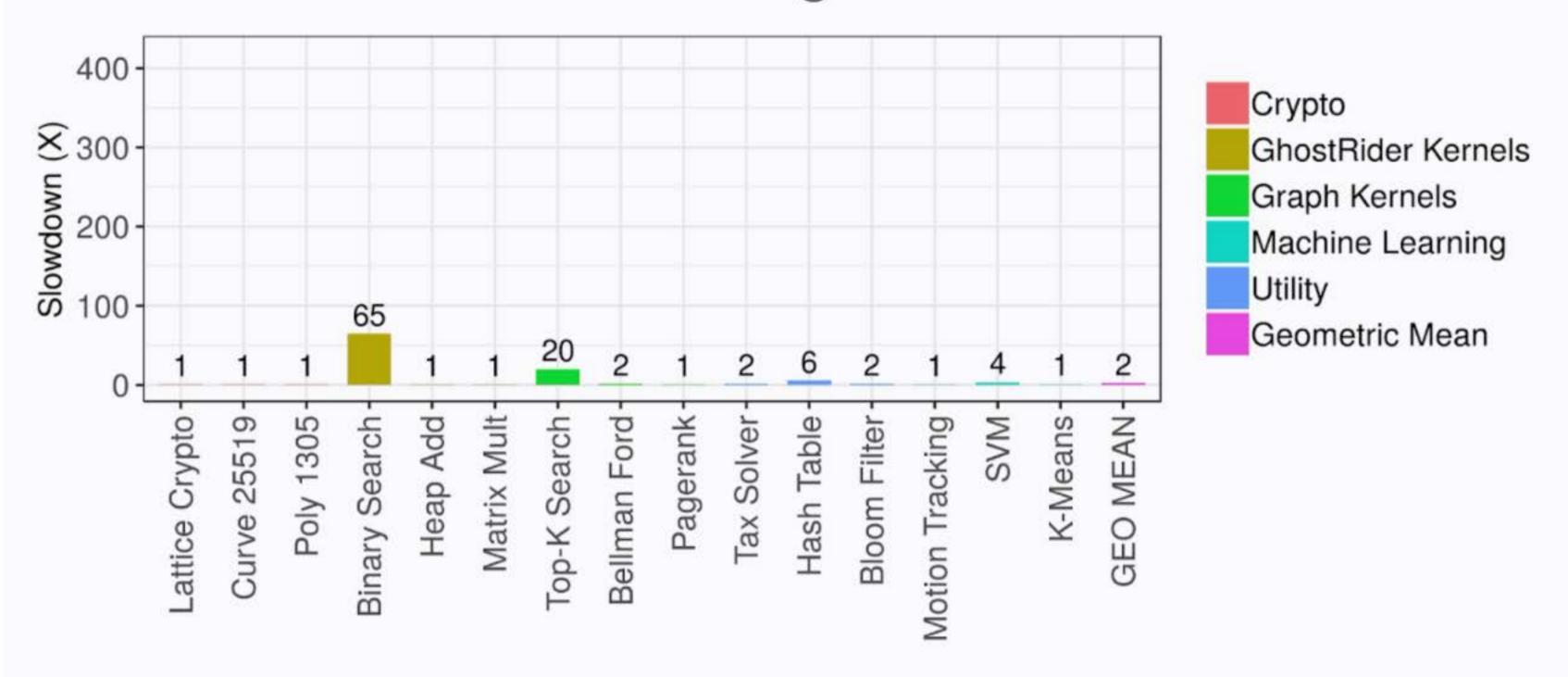

# Our Solution: **Timing** Side Channel

### Our Solution: Microarch. Power Side Channel

### Outline

- Our Solution's Design

- Core Principles that Enable Generalization

- > Performance Comparison

- Future Work

### Our Solution: Microarch. Power Side Channel

## Our Solution: All Digital Side Channels

# Our Solution: **Timing** Side Channel

## Our Solution: All Digital Side Channels

# Our Solution: **Timing** Side Channel

### Outline

- Our Solution's Design

- Core Principles that Enable Generalization

- > Performance Comparison

- Future Work

### Future Work in Side-Channel Defenses

**Automation**

Synthesizing program transformations

Precision

Integrating better models of information leakage Performance

Aggressive compiler optimizations and modest microarch. modifications

such that f ' does not leak information through side channels

#### Synthesizing Side-Channel Defenses

such that f 'does not leak information through side channels

#### Synthesizing Side-Channel Defenses

such that f does not leak information through side channels

Goal: Adapt research in superoptimizers and program synthesis

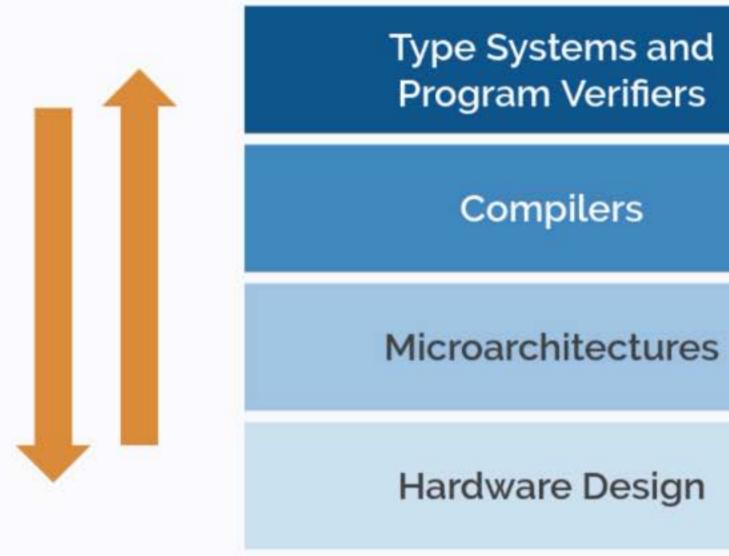

# Synthesis for **Stronger Guarantees**

Microarchitectural Specification

Domain-Specific Language for Compiler Transformations

Executable Code for Program Transformations

# Synthesis for **Stronger Guarantees**

Microarchitectural Specification

Domain-Specific Language for Compiler Transformations

- + Type Analysis + Solver-Based Verification

Executable Code for Program Transformations

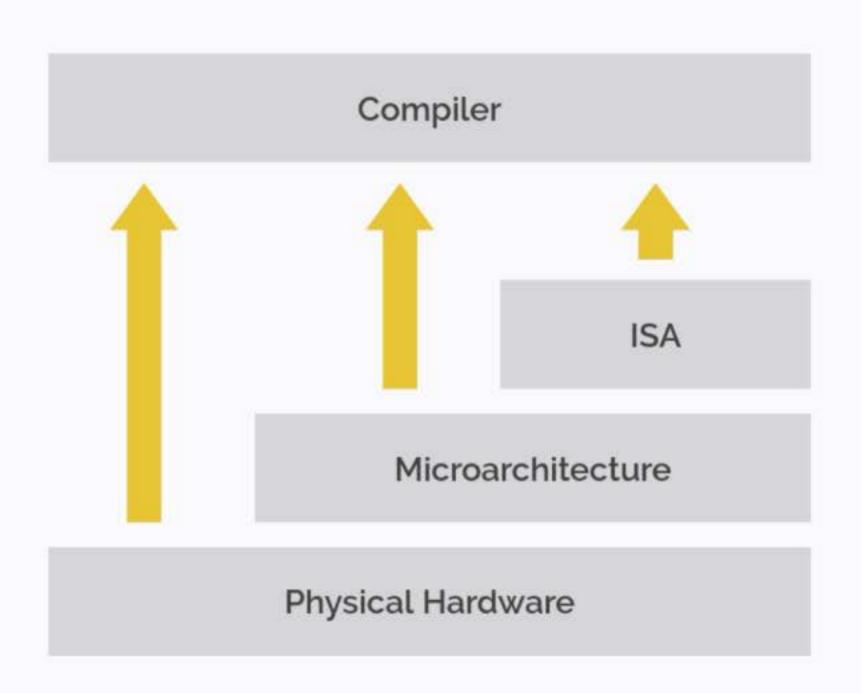

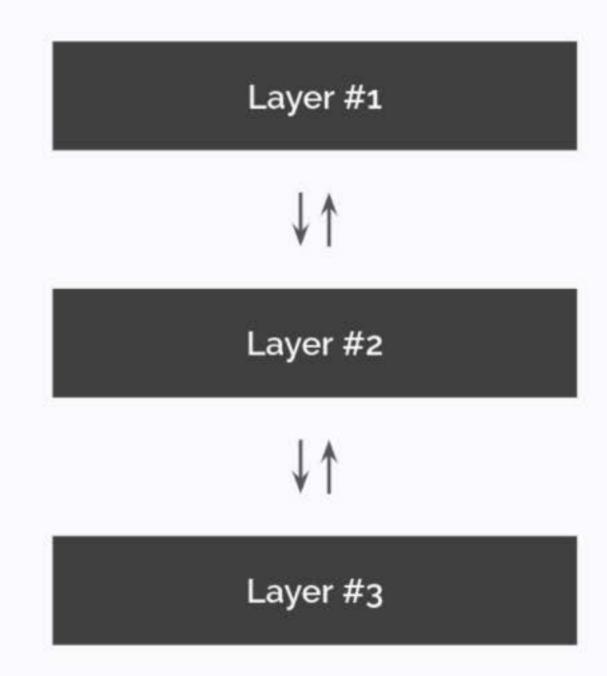

We need to tell compilers about potential side channels.

We need to tell compilers about potential side channels.

Our current approach is an ad-hoc mix of program analysis, statistics, and manual inspection.

We need to tell compilers about potential side channels.

Our current approach is an ad-hoc mix of program analysis, statistics, and manual inspection.

**Goal: Precise** abstractions of underlying layers.

Compilers currently are at the mercy of the ISA.

Compilers currently are at the mercy of the ISA.

We need more control of the microarchitecture and hardware.

Compilers currently are at the mercy of the ISA.

We need more control of the microarchitecture and hardware.

**Goal:** Broaden the definition of the ISA beyond just a functional interface.

Debugging for security sometimes requires knowing a little about the implementation.

Debugging for security sometimes requires knowing a little about the implementation.

But abstractions explicitly disable peeking into the implementation!

Debugging for security sometimes requires knowing a little about the implementation.

But abstractions explicitly disable peeking into the implementation!

This problem affects performance debugging as well.

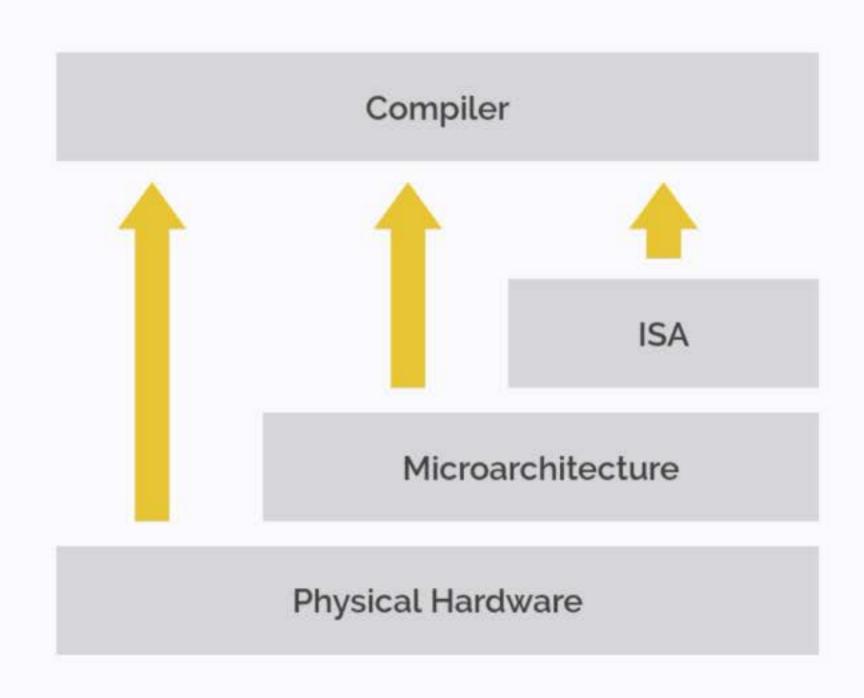

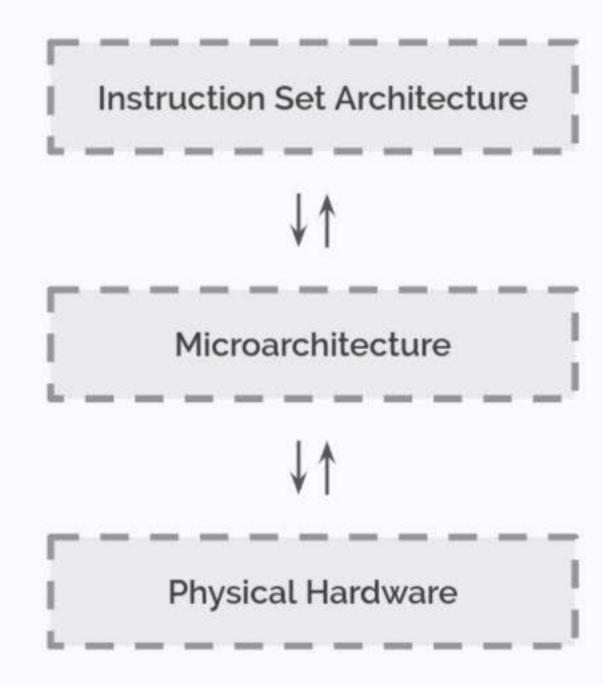

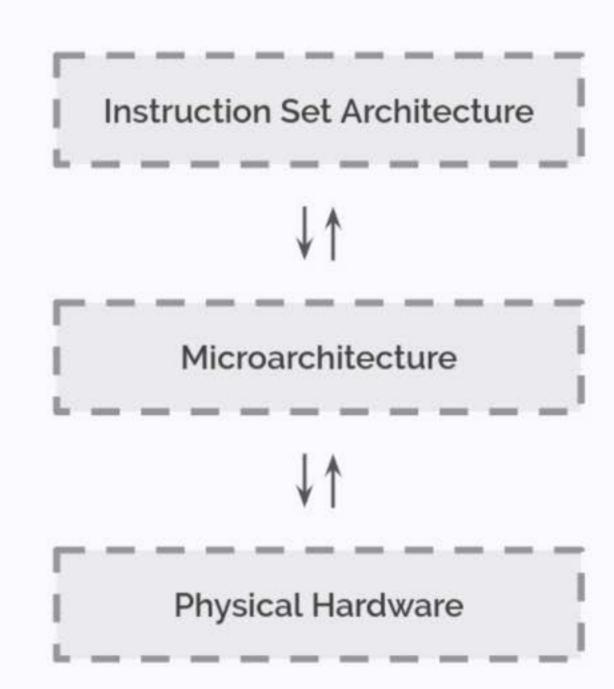

# Peeking Inside the Hardware Implementation

#### Peeking Inside the Hardware Implementation

#### Can assist in:

Discovering Denial-of-Service attacks

Locating Confused-Deputy problems

Tuning performance and energy consumption

Instruction Set Architecture

Microarchitecture

Physical Hardware

#### Peeking Inside the Hardware Implementation

#### Can assist in:

Discovering Denial-of-Service attacks

Locating Confused-Deputy problems

Tuning performance and energy consumption

Instruction Set Architecture

Microarchitecture

Physical Hardware

Instruction Set Architecture

Microarchitecture

Physical Hardware

Functional programming for hardware design [e.g. Cλash, Floh, SHard, and FLaSH]

#### Research Questions:

- How can we quantify security?

- How can we transform programs for energy efficiency?

Functional programming for hardware design [e.g. Cλash, Floh, SHard, and FLaSH]

Instruction Set Architecture

Microarchitecture

Physical Hardware

# Thanks to My Collaborators and Sponsors

Calvin Lin, PhD Advisor, UT Austin

Mohit Tiwari, PhD Advisor, UT Austin

K Rustan M. Leino, Amazon

Chris Hawblitzel, Microsoft Research

Laure Thompson, Cornell University

Joshua Eversmann, Civitas Learning

Greg McDonald, HBK Investments

Bryan Parno, Carnegie Mellon University

Jacob R. Lorch, Microsoft Research

Srinath Setty, Microsoft Research

Manos Kapritsos, University of Michigan

Barry Bond, Microsoft Research

Raymond Chee, Carnegie Mellon University

Varun Adiga and Kasra Sadeghi, UT Austin