#

#### The Wisconsin Quickstep Project

### Jignesh M. Patel

MADISON

#### Blog: http://bigfastdata.blogspot.com

# Good News: Big Data Opportunity

Databases are at the core of the big data revolution

# **Bad News: Big Data Software**

# What we have delivered looks like a pig with lipstick

# **Good News: Big Data Opportunity**

# People are focused on the massive and real growth in this area

# Bad News: The game is up!

We can't hide for much longer

a disruptive way

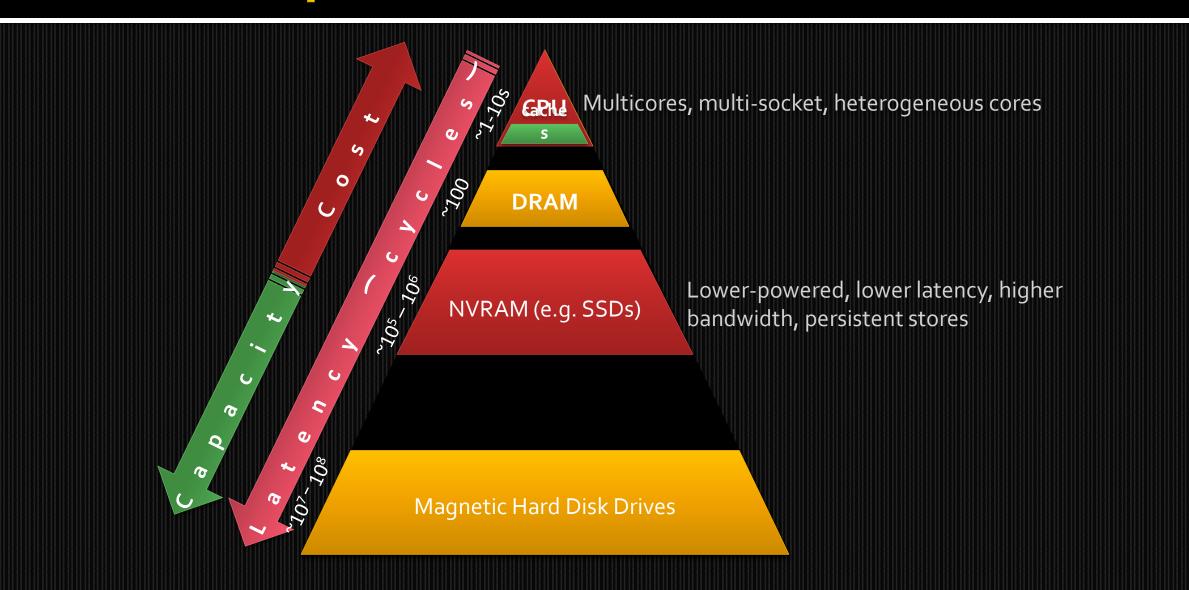

# **Disruptive hardware trends**

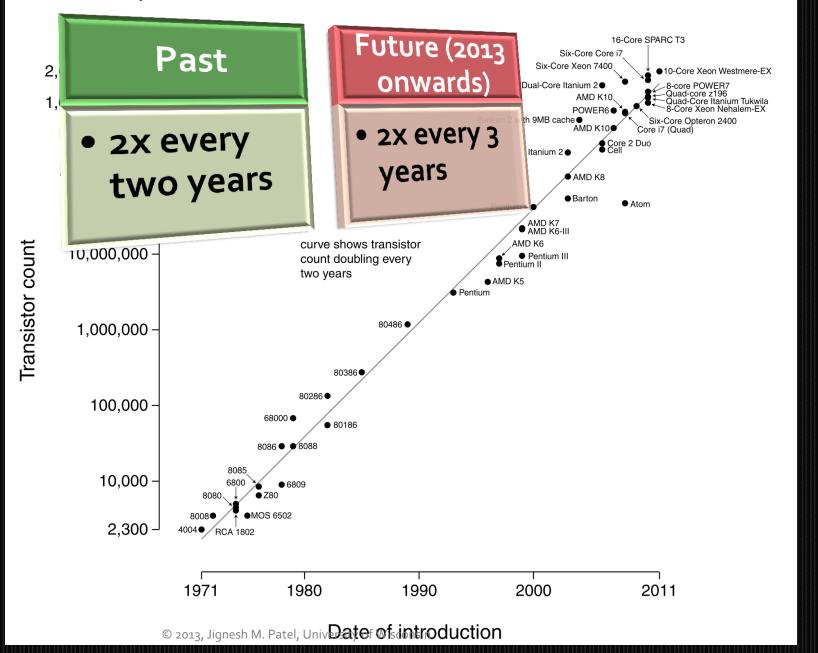

#### Microprocessor Transistor Counts 1971-2011 & Moore's Law

Image credit: Wikipedia

#### Moore's Law continues, but ...

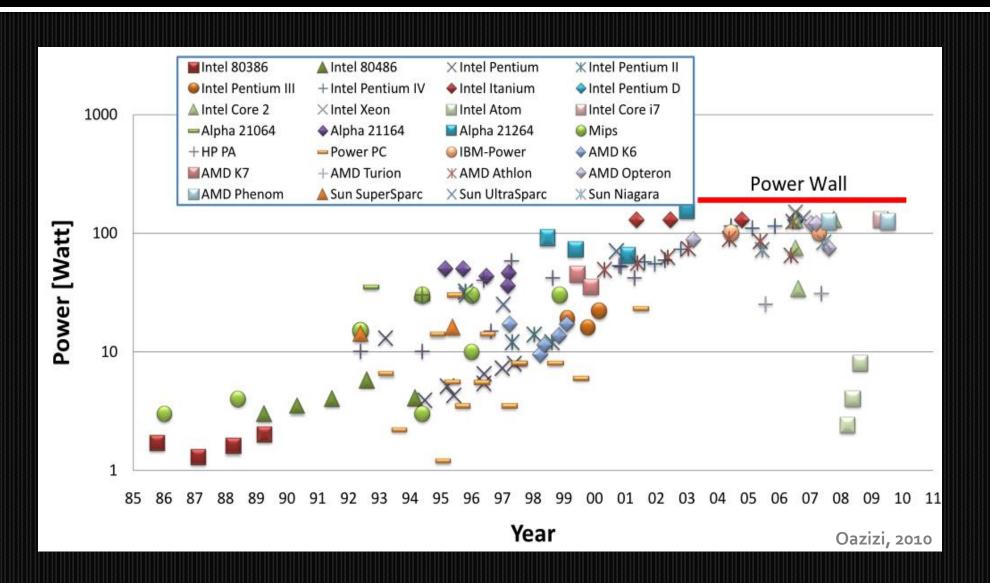

#### What's Next for Processors?

- Future processor design?

- Keep adding cores

(~40% per generation)

- 2. Heterogeneous cores

- 3. Programmable functional units

- But, systems must work within a power budget

- Data growth continues unabated

- Need to do more with less.

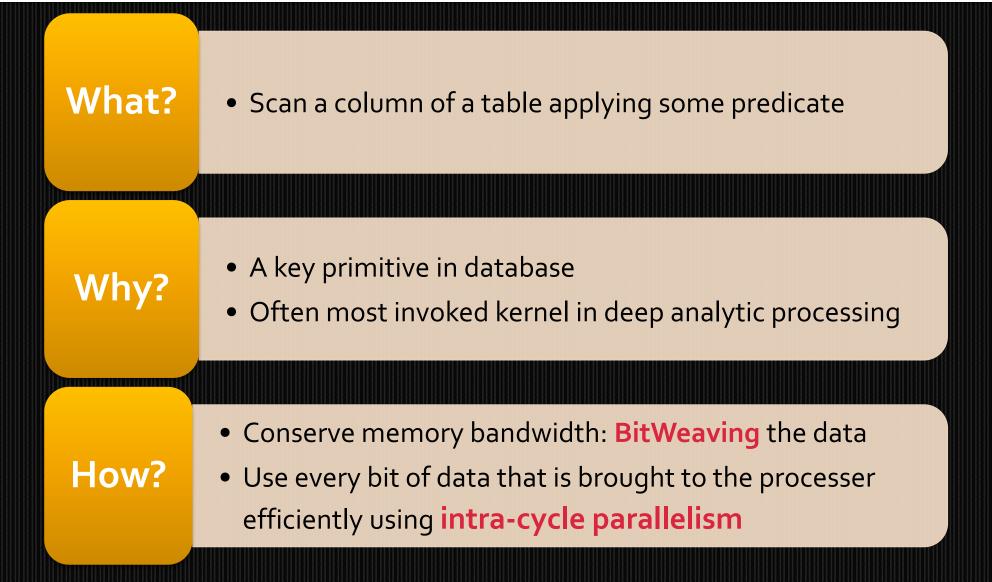

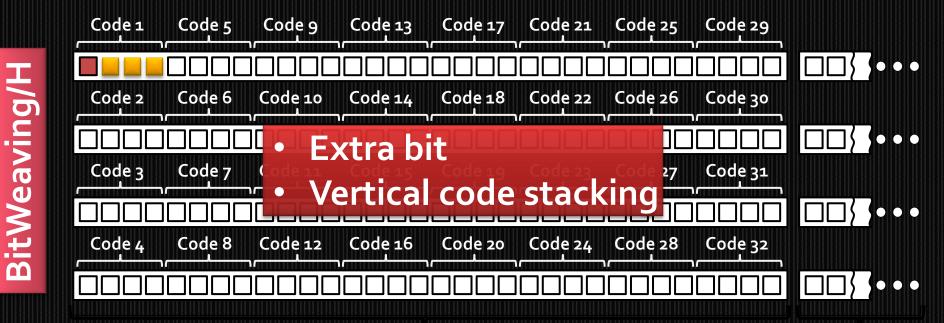

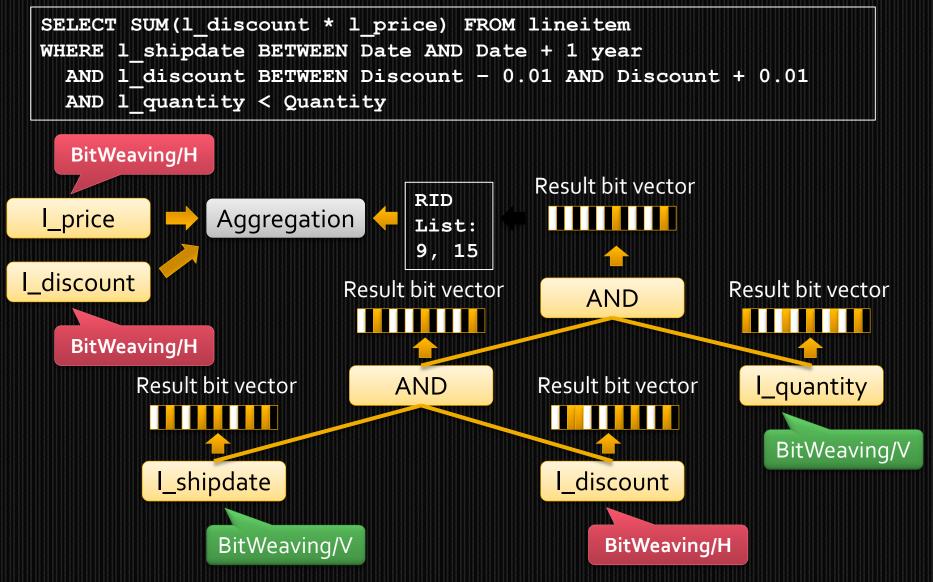

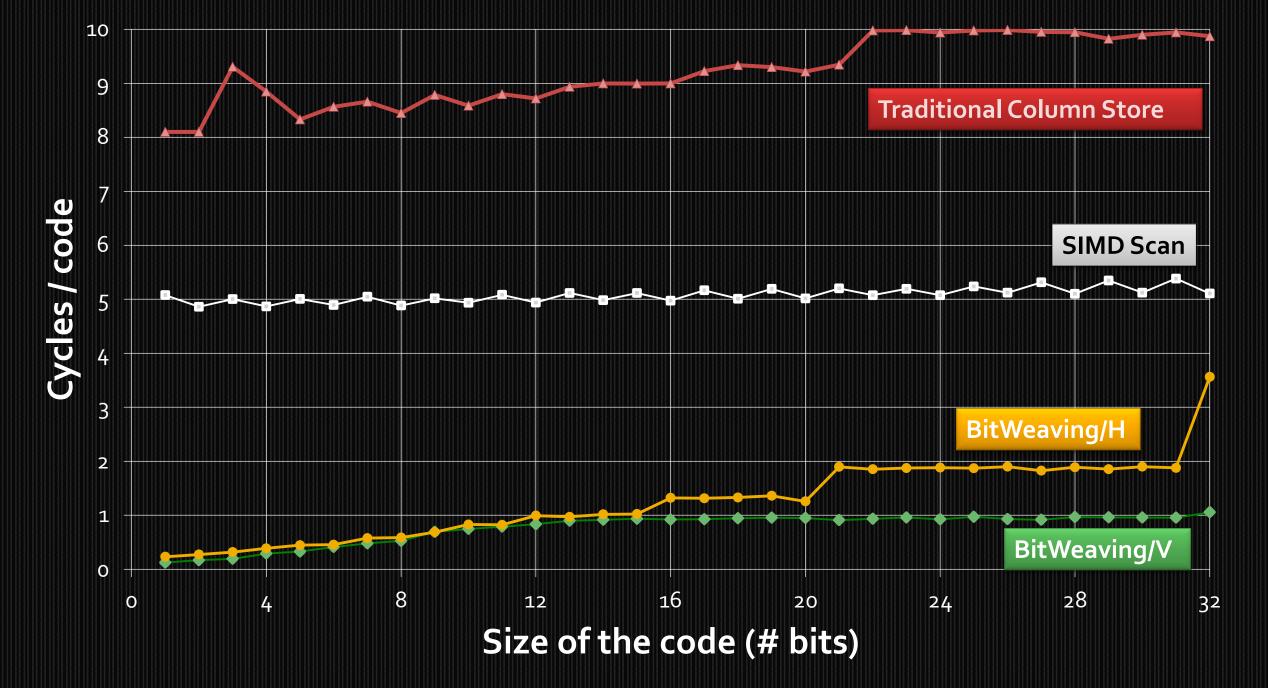

Li and Patel, SIGMOD'13 Scan: A Key Data Processing Kernel

### Focus on Column Scan (can be generalized)

#### **Column Store** Traditional Row Store discount quantity shipdate shipdate discount quantity Mar-12-2013 5% 5 5% Mar-12-2013 5 Jan-08-2013 2% 4 Jan-08-2013 2% 4 10% Apr-29-2013 3 Apr-29-2013 10% 3 May-14-0% 6 6 May-14-0% 2013 2013 . . . . . . . . . 5% . . . ... . . . ... 0 Feb-28-2013 Feb-28-2013 5% File: n-1 File: n 0 Column Codes: 5 3 2 6 4 7 1 0

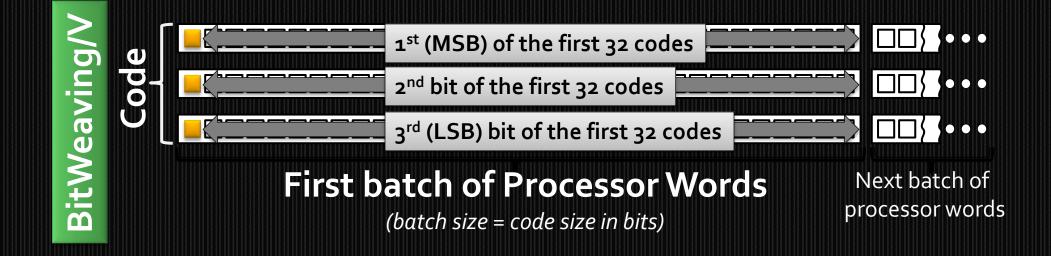

#### First batch of Processor Words

(batch size = code size in bits)

Next batch of processor words

# Framework – Example

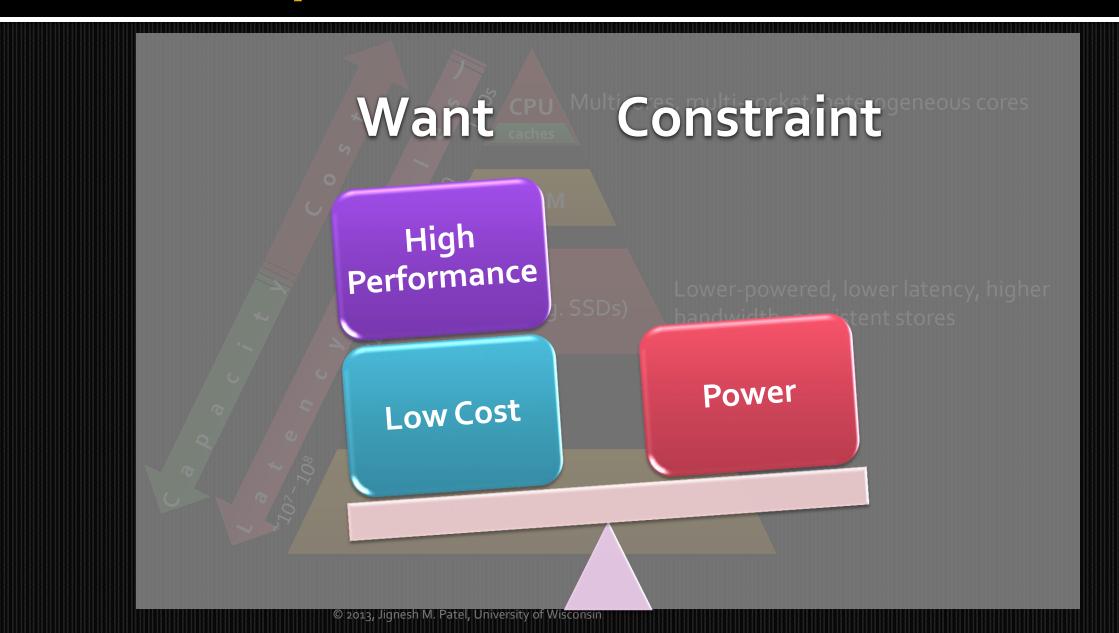

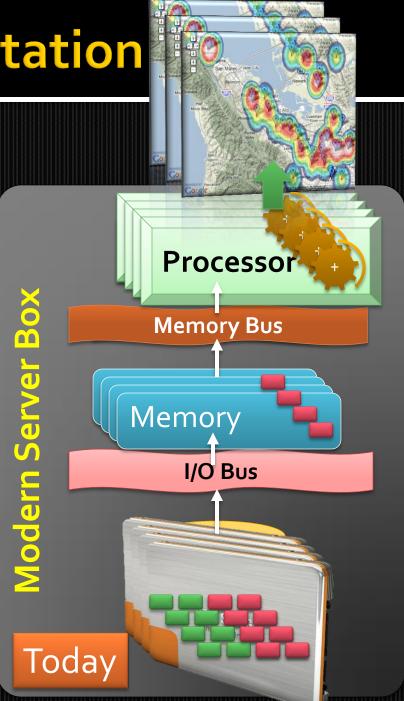

# **Disruptive hardware trends**

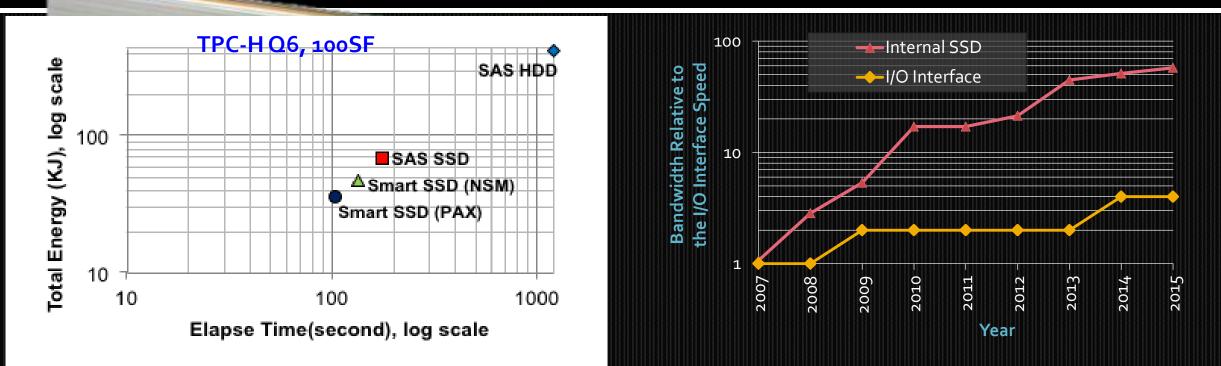

## **Data and Computation**

Long Term: Raw computing and storage costs tends to zero!

The cost is in moving data and powering the circuits/devices

### **Example: Flash SSD Architecture**

There are similar ways of using hardware creatively, e.g. ASICs or GPUs.

#### Basically, need hardware and software synergy!

# Conclusions

Transformative architectural changes at all levels (CPU, memory subsystem, I/O subsystem) is underway

Need to rethink data processing kernels; e.g. BitWeaving

Need to think of hardware software co-design

# Big Data Hardware

## Big Data Software

# Thanks!

# **The Quickstep Team**

Blog: http://bigfastdata.blogspot.com